- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- HyperRAM RWDS and FlexSPI DQS

HyperRAM RWDS and FlexSPI DQS

HyperRAM RWDS and FlexSPI DQS

Hi guys,

I'm looking at the documentation of the FlexSPI and HyperRAM devices, and I don't understand the RWDS(DQS in the IMXRT) timing, when this signal is used as DATA MASK during the write transaction.

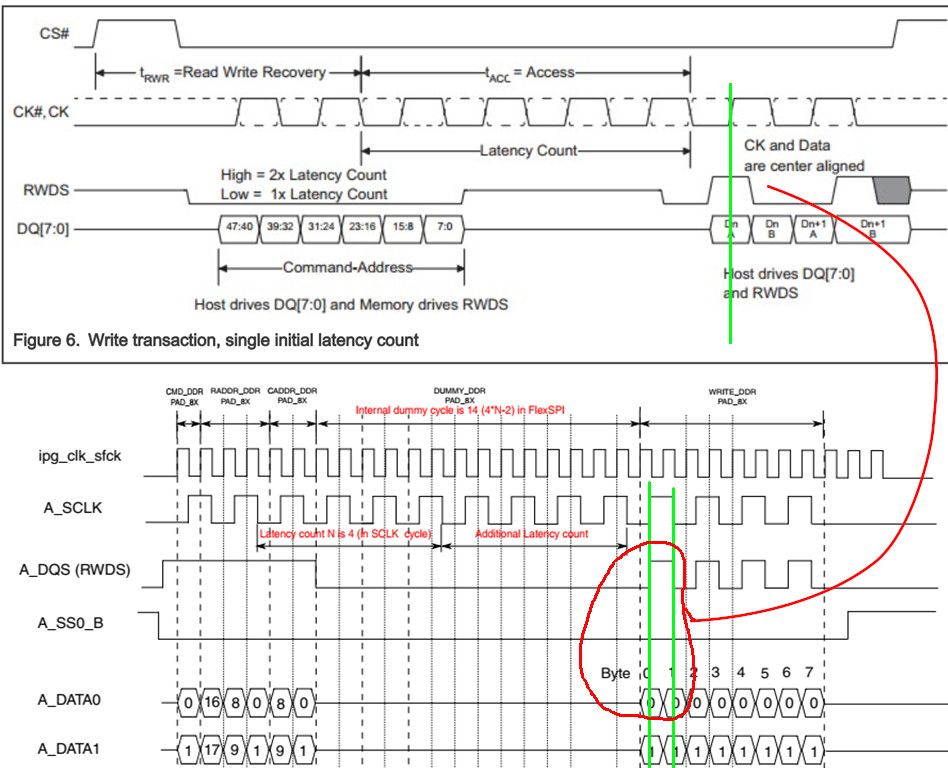

In the attached file JPG file, there are 2 pictures.

The top picture shows the write transaction signaling from hyperRAM's datasheet. The bottom picture shows the FlexSPI signaling for a HyperBus device, taken from IMXRT Ref Manual.

As you can see the RWDS signal is not aligned as shown in the in the HyperRAM's datasheet.

Is the RWDS being used as DATA MASK in the EVKs during write transactions or it is simple held at zero all times?

Thanks a lot

Patricio

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

In my opinion, the above two figures both show CK and Data are center-aligned, however, in the below figure, the RWDS shift a half-cycle phase versus the above figure.

About using the HyperRAM with the i.MX RT, to provide the fastest possible support, I'd highly recommend you refer to the application note and its corresponding code.

corresponding code.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------