- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- FLEX IO in low power run mode (RT1015)

FLEX IO in low power run mode (RT1015)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

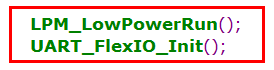

Hi,

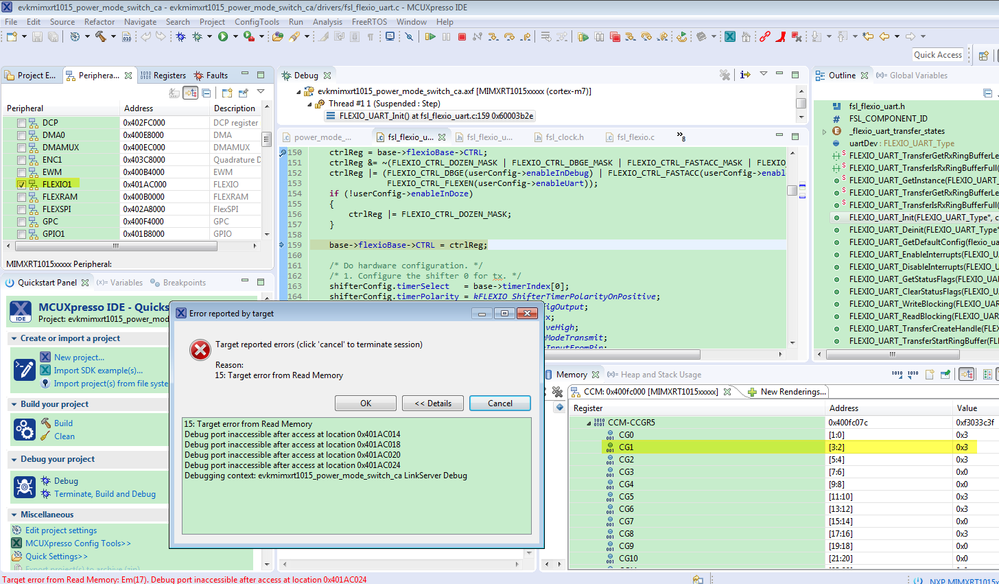

I am testing UART Flex IO in low power run mode in 1015RT.

I use the SDK sample and combine UART Flex IO sample.

Please see my attachment.

My code hang up when UART_FlexIO_Init,

As I know, Flex IO can use in low power mode.

What is the correct way to use UART_FlexIO in low power run mode?

Any limitation?

Or any suggestion?

Thanks

Ken

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken Su,

A lot of talks with an internal side, it turns out the document error.

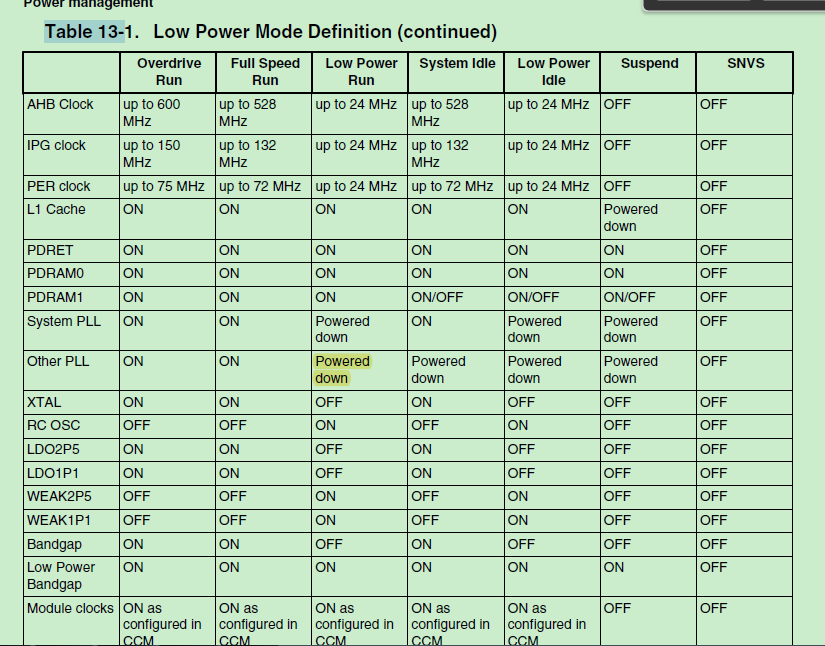

1. PLLs for FlexIO is powered down under low power run mode

Please check the RT1050RM, RT1015RM still didn't update it, AN12345 is also incorrect, already report it.

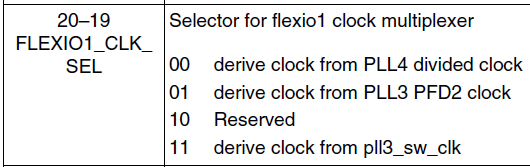

2. pll3_sw_clk_sel =1 option should not be used, That bit is intended for NXP internal test and uses an input clock on a pin instead of the internal PLL bypass clock. So it is a different kind of bypass than what is implied in the description.

This part will be removed from the document.

3. The FlexIO module allows for functional clock to run in low power modes (and really this statement is a carry over from Kinetis), but the SOC integration on RT10xx parts does not.

I also suggest our related department to add peripheral states to the low power mode definitions table.

In conclusion, FlexIO module can't be used under low power run mode.

Sorry for the inconvenience we bring you.

If you still have questions about it, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken Su ,

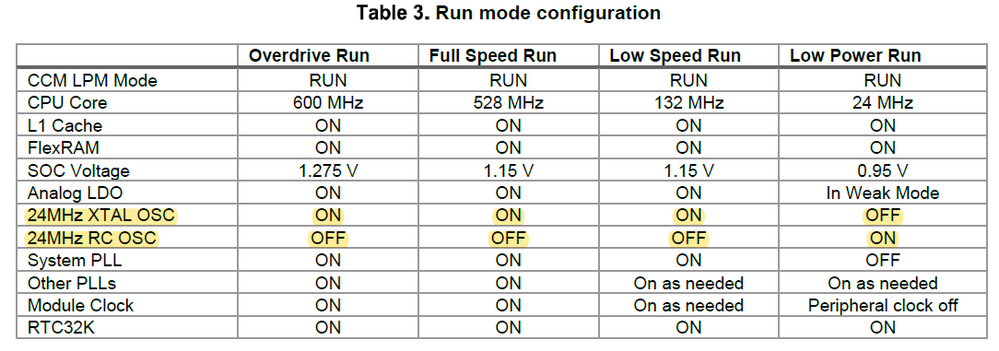

Please check the RT1015 power consumption application note at first:

https://www.nxp.com/docs/en/application-note/AN12345.pdf

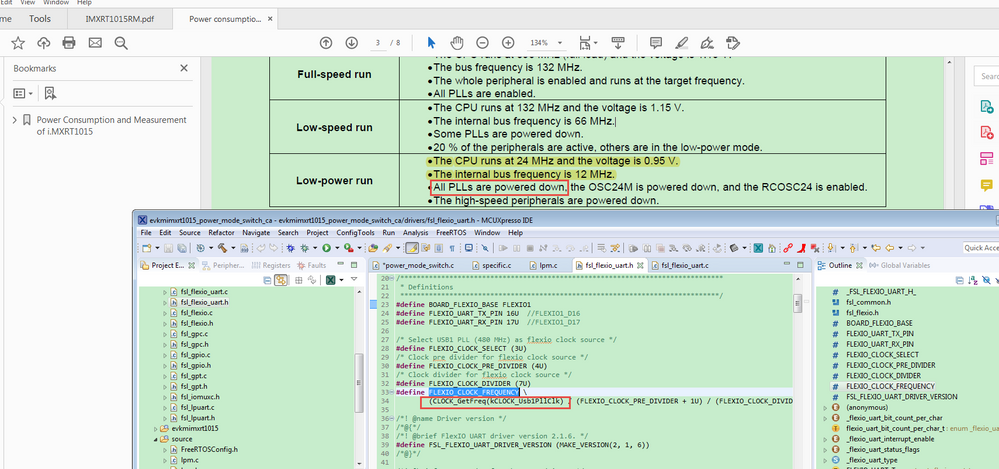

Then check your code, your code FLEXIO is using the usbPLLclk, but from the application note, you can find in the low power run mode, all the PLLS are powered down, that's why you hang up there.

So, you need to check other clock source for flexio which still works under low power run mode.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry

Thanks for your remind,

Frankly speaking, I don't know very well about the CLK setting,

Could you let me known how to use FlexIO in low power run mode?

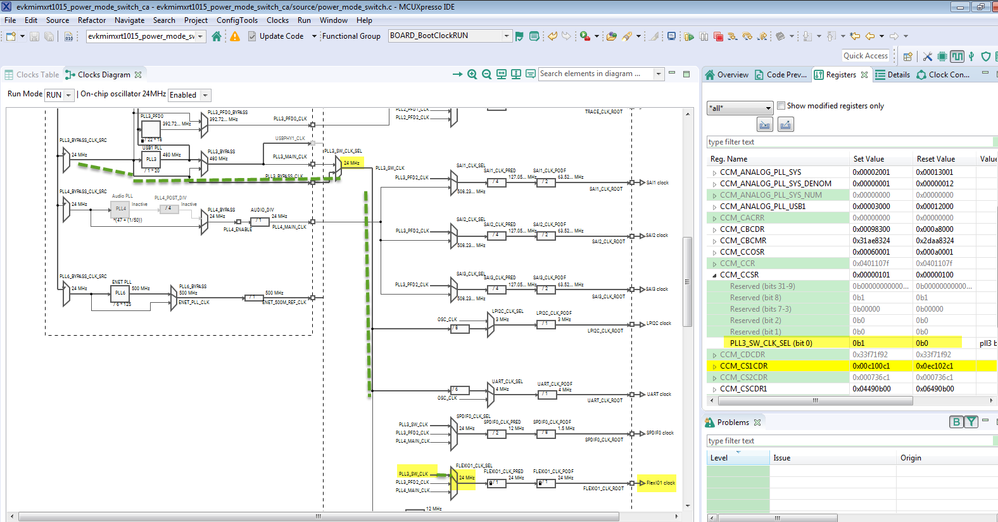

I think it need to change FLEXIO1_CLK_SEL to OSC so that I can use FlexIO UART in low power run.

Is it possible?

Regards

Ken

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken Su,

Thanks for your updated information.

Today, I do the testing, bypass the PLL3, and select the FlexIO1 clock source as PLL2_SW_CLK, PLL2_SW_CLK bypass the PLL3, and from the 24Mhz directly, but it seems still have an issue when I enable the FlexIO1 clock gate and access the FLEXIO1 register.

Anyway, I will help you to check it internally.

If I get valuable information, I will also let you know.

Please keep the patient, thanks.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry

Thanks a lot for your support.

I will wait.

Best Regards

Ken

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken Su,

Get the internal response: Unfortunately, the FlexIO cannot be used in low power run mode.

But more details, I am still checking more deep level.

Please keep the patient!

Best Regards.

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry

OK, I understood.

I will wait your information.

Thanks.

Best Regards

Ken

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken Su,

A lot of talks with an internal side, it turns out the document error.

1. PLLs for FlexIO is powered down under low power run mode

Please check the RT1050RM, RT1015RM still didn't update it, AN12345 is also incorrect, already report it.

2. pll3_sw_clk_sel =1 option should not be used, That bit is intended for NXP internal test and uses an input clock on a pin instead of the internal PLL bypass clock. So it is a different kind of bypass than what is implied in the description.

This part will be removed from the document.

3. The FlexIO module allows for functional clock to run in low power modes (and really this statement is a carry over from Kinetis), but the SOC integration on RT10xx parts does not.

I also suggest our related department to add peripheral states to the low power mode definitions table.

In conclusion, FlexIO module can't be used under low power run mode.

Sorry for the inconvenience we bring you.

If you still have questions about it, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry

It's OK.

Very appreciate for your detail information.

Regards

Ken

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken Su

You are always welcome!

If your question is solved, please help me to mark the correct answer, just to close this case, thanks.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------