- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: understanding iomuxing imx6QD

understanding iomuxing imx6QD

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

understanding iomuxing imx6QD

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

We are working on imx6q processor board and want to understand iopin muxing in detail. for this we have refereed to imx6q-pinfun.h file

for example: it states:

| #define MX6QDL_PAD_CSI0_MCLK__IPU1_CSI0_HSYNC | 0x25c 0x62c 0x000 0x0 0x0 |

| #define MX6QDL_PAD_CSI0_MCLK__CCM_CLKO1 | 0x25c 0x62c 0x000 0x3 0x0 |

| #define MX6QDL_PAD_CSI0_MCLK__GPIO5_IO19 | 0x25c 0x62c 0x000 0x5 0x0 |

| #define MX6QDL_PAD_CSI0_MCLK__ARM_TRACE_CTL | 0x25c 0x62c 0x000 0x7 0x0 |

where it staed that the pin function ID is a tuple of

<mux_reg conf_reg input_reg mux_mode input_val>

if i take one example from above let's say :

| #define MX6QDL_PAD_CSI0_MCLK__CCM_CLKO1 | 0x25c 0x62c 0x000 0x3 0x0 |

if i look the reference manual, then mux-reg for CSI0_MCLK is IOMUXC_SW_MUX_CTL_PAD_CSI0_HSYNC (Address: 20E_0000h base + 25Ch offset = 20E_025Ch) offset is 0x25c

conf_reg for CSI0_MCLK is IOMUXC_SW_PAD_CTL_PAD_CSI0_HSYNC (Address: 20E_0000h base + 62Ch offset = 20E_062Ch), so offset is 0x62c

MUX-Mode i need select from IOMUXC_SW_MUX_CTL_PAD_CSI0_HSYNC whose value 011 (0x3)

So

| #define MX6QDL_PAD_CSI0_MCLK__CCM_CLKO1 | 0x25c 0x62c 0x000 0x3 0x0 |

in above macro i got 0x25c 0x62c 0x3 but what about values of input_reg (0x000) and input_val (0x0) ??????? how to get them correctly?????

and also if iam using them in my dts for iomux

for example say :

mipi_csi {

pinctrl_mipi_csi_1: mipi_csipgrp-1 {

fsl,pins = <

MX6QDL_PAD_CSI0_MCLK__CCM_CLKO1 0xb0b1

>;

};

};

in above 0xb0b1 is the value taken from IOMUXC_SW_PAD_CTL_PAD_CSI0_HSYNC.

which is the value we should take. is taking SW_PAD_CTL_PAD value be sufficient?????

Please reply...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

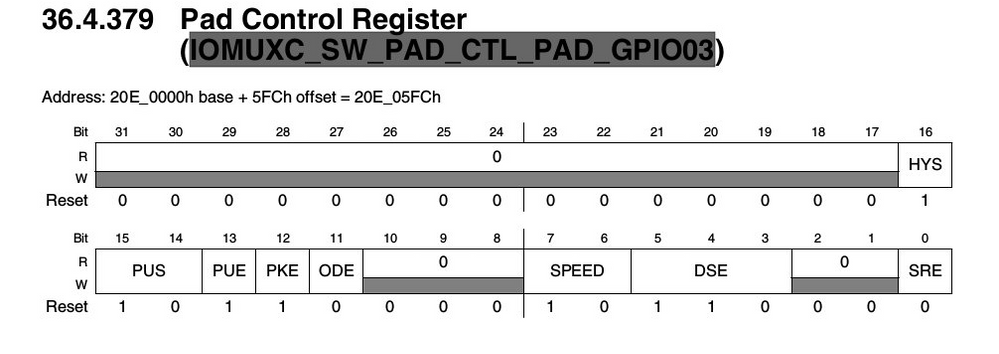

I would like understand briefly how to get the values for io pin muxing like

For ex:

I take taken dts file of some reference design where they are using :

| MX6QDL_PAD_GPIO_3__CCM_CLKO2 | 0x000b0 |

from the above ,

HYS=0 CMOS input, How we will come to know whether we require CMOS input or schmitt trigger input (or by trial error method)

PUS=00 100K Ohm pull-down (how to get this value from schematic, whether we require Pull up or pulldown and choose between 100 K PU, 100 K PD, 22K PU, 47K PU ????)

PUE = 0 (how choose between keeper and puller)

PKE= 0 (pull /keeper enable disable. how choose ????)

Speed =(how to choose the correct speed required?????

DSE (Drive Strength how to choose correct values????)

MX6QDL_PAD_GPIO_3__CCM_CLKO2 0x000b0

whether they have arrived at 0x000b0 by trial and error method or how to derive it exactly ????

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I Checked in Reference Manual, But it is just confusing.

for Some Values like : (as an example)

| MX6QDL_PAD_CSI0_DAT12__IPU1_CSI0_DATA12 | 0x80000000 |

Here We need to check SW_PAD_CTL_CSIO_DAT12

Bit 16 -HYS is selectable

Bit 15 14 -PUS

like that. But how they have made bit 31 as 1 (0x80000000)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The 0x80000000 means that the kernel will not touch the PAD settings and

it will use whatever comes from default (or from U-boot in case it was

previously configured in U-boot).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I know it's been a long time since you replied this question but can you point me to the source of this 0x80000000 value?

More precisely I'd like to know if it's only the PAD_CTL that is unchanged or the MUX_CTL setting as well?

For example MX6QDL_PAD_EIM_D22__GPIO3_IO22 is supposed to set the EIM_D22 PAD as GPIO (ALT5) but after changing u-boot to use USB OTG it seems that PAD_EIM_D22 is now configured as USB_OTG_PWR (ALT4) and MX6QDL_PAD_EIM_D22__GPIO3_IO22 0x80000000 seems to do nothing about that as I still read 4 when typing devregs 0x020e00a8 (MUX_CTL).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Srinivasa

input_reg and input_val are address offsets for daisy chain register (IOMUXC_xxx_SELECT_INPUT)

and its value (if it presents for that signal). Regarding SW_PAD_CTL_PAD value you should check

description in RM and choose appropriate for your needs value.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------