- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: iMX8mp gpio configuration

iMX8mp gpio configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello

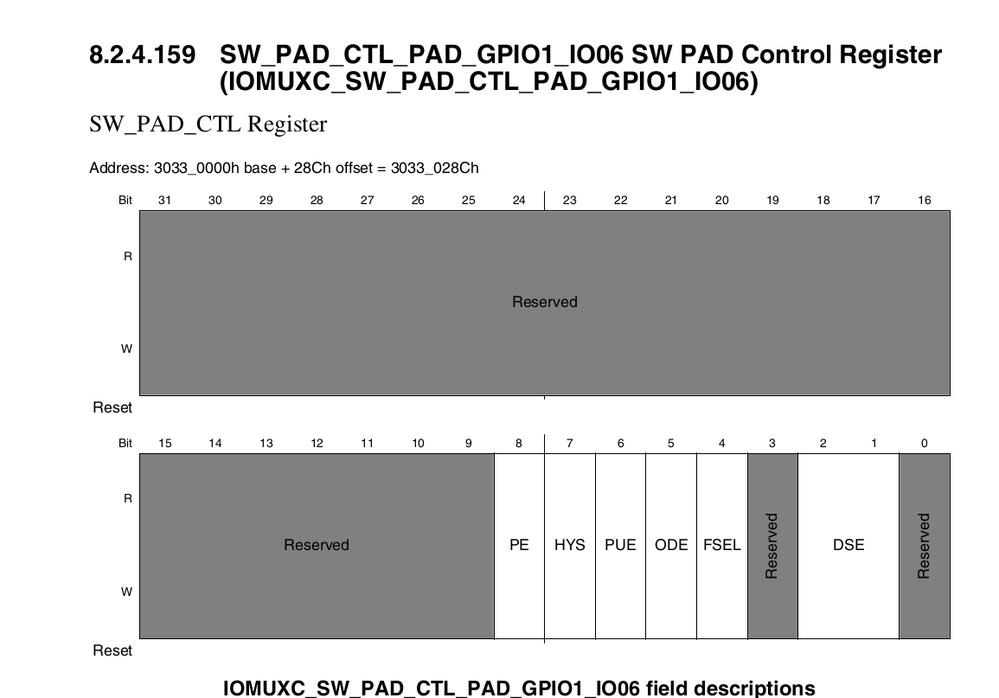

could you please help me out to configure GPIO1_IO6 with internal PULLUP . below are the DTB contents i found relevant to the GPIO configuration which i'll be using in my driver.

By default we are getting line in pulled LOW state now. we need to configure in pulled high state by default.

/*

* The pin function ID is a tuple of

* <mux_reg conf_reg input_reg mux_mode input_val>

*/

#define MX8MP_IOMUXC_GPIO1_IO06__GPIO1_IO06 0x02C 0x28C 0x000 0x0 0x0

&iomuxc {

pinctrl_csi0_rst: csi0_rst_grp {

fsl,pins = <

MX8MP_IOMUXC_GPIO1_IO06__GPIO1_IO06 0x19

>;

};

};

to my understanding the value 0x19 is writing to the below control register which is setting the GPIO to use as PULLDOWN.

where bit no:8 =0 and bit no:6=0.

is this the right approch, please help me understand it correctly.

Thanks in advance

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mukesh

> my understanding the value 0x19 is writing to the below control register which is

>setting the GPIO to use as PULLDOWN. where bit no:8 =0 and bit no:6=0.

for enabling pull resistor set bit no:8 =1

enable pull down(LOW) bit no:6=0

enable pull up(HIGH) bit no:6=1

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi igor,

Thank you for replying to the issue.

I changed the value as 1 at bit number 6 and bit number 8 , but it seems not taking any effect to change as internal pullup

&iomuxc {

pinctrl_csi0_rst: csi0_rst_grp {

fsl,pins = <

MX8MP_IOMUXC_GPIO1_IO06__GPIO1_IO06 0x159

>;

};

};

for confirmation I tried reading register address 0x3033028C using devmem2, but it thrown a error mentioning bad address.

can you please answer the following queries

1.Does the control register I'm referring to is correct?

2.what is the correct physical address of the register that refer the preprocessor directive MX8MP_IOMUXC_GPIO1_IO06__GPIO1_IO06 ?

3.At the defination of this preprocessor directive the tuple contains a member named input_val, is it input to mux_reg or conf_reg ?

/* <mux_reg conf_reg input_reg mux_mode input_val>

*/

#define MX8MP_IOMUXC_GPIO1_IO06__GPIO1_IO06 0x02C 0x28C 0x000 0x0 0x0

can you please answer these queries,

Thank you,

Mukesh kumar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

devmem2 is not supported by nxp, please try memtool

https://source.codeaurora.org/external/imx/imx-test/tree/test/memtool?h=lf-5.10.y_2.0.0

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi igor,

I'm able to see that register contents are updating properly,

i also changed the drive strength field as well from X1 to X6 that helped to drive the pullup to 1.8V for me.

while the drive strength field is set X1 the pullup is able to drive 0.5V only.

thanks for the help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mukesh

> my understanding the value 0x19 is writing to the below control register which is

>setting the GPIO to use as PULLDOWN. where bit no:8 =0 and bit no:6=0.

for enabling pull resistor set bit no:8 =1

enable pull down(LOW) bit no:6=0

enable pull up(HIGH) bit no:6=1

Best regards

igor