- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

iMX8M mini DDR4 data bits swap

Hi,

we have a custom design based on i.MX8 with a DDR4 memory.

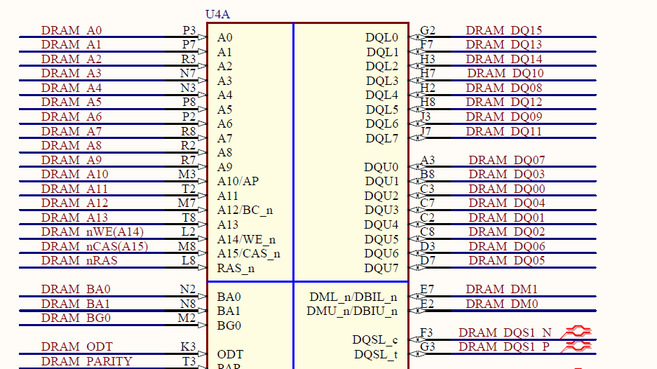

we customized the design so that the i.MX8M DDR4 data lines are swapped and not routed directly to the DDR4 in the same order of pins, for ex:

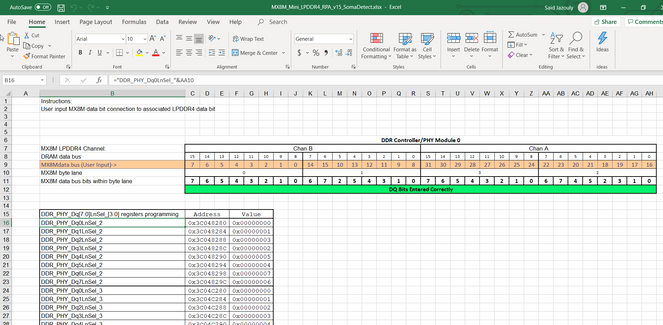

In a previous design where we used LPDDR4 memory, we had a special tab in the excel tool MX8M_Mini_LPDDR4_RPA_v15 to make the bit swapping:

However we don't have such a tab in the DDR4 tool MX8M_Mini_DDR4_RPA_v11

- How can we perform the data bit swapping in this case?

- Is it possible to do a complete DDR4 configuration and perform the stress tests and get the timings using "Config Tools for i.MX v7"

- Any helpful procedure that we can follow?

Thanks very much.

Thank you for the reply.

Good to know that there are no limitations on swapping the DDR4 data lines, however how do we tell the DDR4 tool MX8M_Mini_DDR4_RPA_v11 to do the DQ lanes swapping in order to start a DDR4 stress test for our custom design?

attached is the MX8M_Mini_DDR4_RPA_v11 file we use.

thank you!

Hi saidjazouly ,

For iMX8MM-EVK, we have 2 versions, one is i.mx8mm + lpddr4, the other is imx8mm+DDR4. attachment is 8MMINID4-EVK-DESIGNFILES. you can refer to it to design your product.

For DDR4, there is no restriction on the exchange of data bits, as you can see in this design files.

Have a nice day!

B.R,

weidong