- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

iMX8M Mini not booting up as VDD_DRAM is not getting required power by PCA9450AAHNY PMIC.

Hello,

We are using iMX8M Mini in our project which is powered up by PMIC PCA9450AAHNY and we are facing issue with boot up.

The difference we observed between the boards which are booting up properly and the ones which are not is that, the former boards are getting expected voltage at VDD_DRAM rail, as per values set in register, of 0.95V from PMIC (BUCK3) whereas the ones which are not booting up is sourced by 0.85V from PMIC (BUCK3) which is default value generated by PMIC (BUCK3).

We're using LPDDR4 at 1.5GHz (DDR clock) frequency which requires typically 0.95V hence we doubt that since it is not getting required power it is hindering booting process. We suspect that patch from SDK for PMIC provided by NXP is not executed

Below is the part of SDK implemented for BUCK3:

/* BUCKxOUT_DVS0/1 control BUCK123 output */

pmic_reg_write(p, PCA9450_BUCK123_DVS, 0x29);

/* Also, set B3_ENMODE=2 (ON by PMIC_ON_REQ=H & PMIC_STBY_REQ=L) */

pmic_reg_write(p, PCA9450_BUCK3OUT_DVS0, 0x1C);

pmic_reg_write(p, PCA9450_BUCK3CTRL, 0x4A);

It would be great if anyone can guide us through this and help with possible solution for the same or suggest if any changes are to be made.

Thanks in advance.

Regards,

Zeel Shah

Thanks @linda_zhang for your response but we are not using the same PMIC as that of yours, so not sure if your configuration can help much.

Just FYI, even we've set the values of registers in same sequence and way as that of yours though 0.95V is not obtained on board as it should be as per register settings.

Regards,

Zeel Shah

Hi community,

I would be grateful if anyone can guide me through this.

Looking forward to your suggestions.(@Yuri , @AllanAn , @guoweisun)

Thanks & Regards,

Zeel Shah

Hi Zeel,

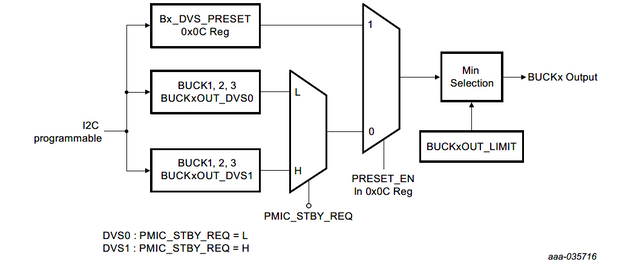

BUCK3 output logic is shown as below, I have checked your I2C command, it is OK to configure BUCK3 as 0.95V.

so I suggest to check:

Whether I2C command has been configured to PCA9450AA successfully or BUCK3 voltage configuraiton changed afterwards.

- read back the register for confirmation,

- Configure BUCK123_DVS as 0xAB to see if BUCK3 follow Bx_DVS_PRESET configuration.

if the 2 action did not valid, please check external hardware connected to see if BUCK3 voltage is affected by external componts.

Brs

Allan