- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

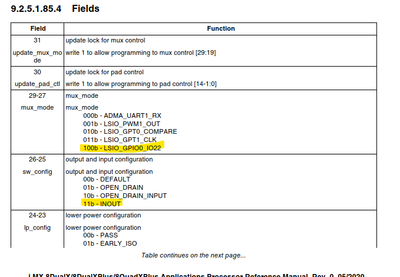

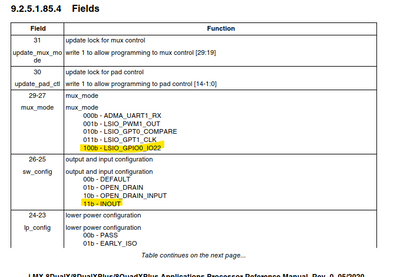

I'm trying to use UART1_RX (ball L31) on an i.MX8XQuadPlus processor. I have the device tree pinctrl setup as follows:

IMX8QXP_UART1_RX_LSIO_GPT1_CLK 0x26000060 // IMX8_FREQ_IN

This should be GPIO0 pin 22:

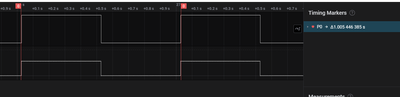

I have a 1 Hz square wave being fed into this pin.

But when I try to read this pin in Linux it always reads low:

root@imx8qxpdeere:~# gpioget gpiochip0 22

0

root@imx8qxpdeere:~# gpioget gpiochip0 22

0

root@imx8qxpdeere:~# gpioget gpiochip0 22

0

root@imx8qxpdeere:~# gpioget gpiochip0 22

0

root@imx8qxpdeere:~# gpioget gpiochip0 22

0

root@imx8qxpdeere:~# gpioget gpiochip0 22

0

root@imx8qxpdeere:~# gpioget gpiochip0 22

0I looked through the errata and didn't see any mention of a GPIO pin.

Any ideas?

已解决! 转到解答。

I had copied and pasted the wrong #define:

#define IMX8QXP_UART1_RX_LSIO_GPT1_CLK IMX8QXP_UART1_RX 3

#define IMX8QXP_UART1_RX_LSIO_GPIO0_IO22 IMX8QXP_UART1_RX 4

I used the former, when I meant to use the later.

I had copied and pasted the wrong #define:

#define IMX8QXP_UART1_RX_LSIO_GPT1_CLK IMX8QXP_UART1_RX 3

#define IMX8QXP_UART1_RX_LSIO_GPIO0_IO22 IMX8QXP_UART1_RX 4

I used the former, when I meant to use the later.