- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX8 LPDDR4 how to change DDR clock

i.MX8 LPDDR4 how to change DDR clock

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX8 LPDDR4 how to change DDR clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using i.MX8MQ with LPDDR4, using DDR Controller Configuration Spreadsheet we could able to configure the DDR clock to 1600,800,334,and 200MHz.

how can we configure the DDR clock to 225MHz? what is the formula to be used.

Regards,

Manoj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Don't try to use other frequency points less than 334MHz if they enable PLL and don't try to use other frequency points than 200MHz and 50MHz if they use PLL bypass mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

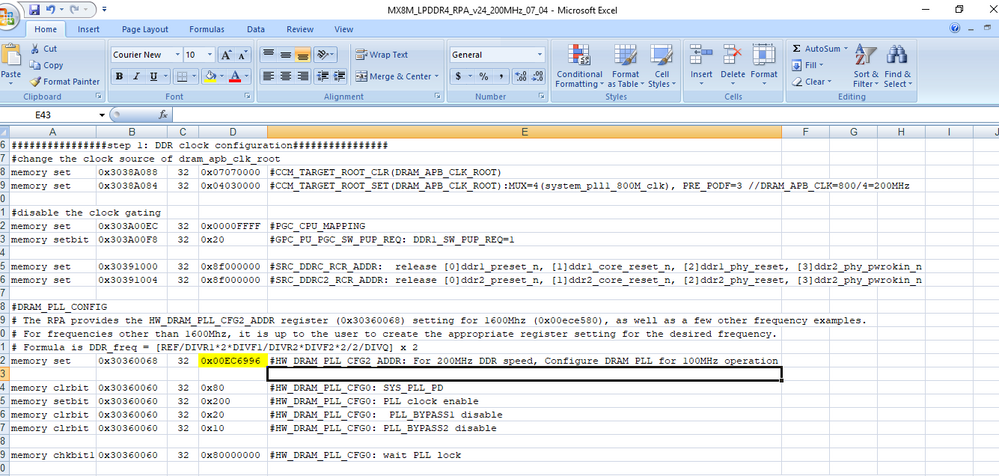

iMX 8M Mini Register Programming Aid DRAM PLL setting

DDR clock set you can refer to this

This link is for iMX8M mini and it's not talking about HW_DRAM_PLL_CFG2_ADDR PLL configuration for iMX8M

Don't try to use other frequency points less than 334MHz if they enable PLL and don't try to use other frequency points than 200MHz and 50MHz if they use PLL bypass mode.

We want to configure DDR at 225MHz or 200MHz and pllbypass is disabled is it ok?

Regards,

Manoj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manoj,

About your above question, You can also use the same method for i.MX8MQ, our expert send it to me.

If you want to use the 225MHZ, so sorry about it, this frequency can not work. I confirm with our expert again.

If customer want to use the frequency below 334MHZ, they must use the PLL bypass mode and only can use the 200MHz and 50MHz this two frequency.

200MHz and 50MHz PLL bypass mode is official supported in DDR script.

200MHz and 50MHz DDR clock means 400MTS and 100MTS DDR data rate.

Hope this can really do help for you.

Have a nice day

Best Regards

Rita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rita,

Ok, If we want to use 200MHz frequency, we should use PLL bypass mode, right?

How we can enable this? excel sheet says PLL_BYPASS disable

And when we are using this value, we could see kernel hang at the below point.

----------------------------------------------------

U-Boot SPL 2018.03-svn73 (Apr 06 2020 - 17:08:22 +0530)

PMIC: PFUZE100 ID=0x10

DDRINFO: start lpddr4 ddr init

DRAM PHY training for 400MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 400MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 100MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 400MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

Trying to boot from MMC1

U-Boot 2018.03-svn73 (Apr 06 2020 - 17:08:22 +0530)

CPU: Freescale i.MX8MQ rev2.0 1500 MHz (running at 1000 MHz)

CPU: Commercial temperature grade (0C to 95C) at 56C

Reset cause: POR

Model: Freescale i.MX8MQ MAGIK2

DRAM: 4 GiB

TCPC: Vendor ID [0x1fc9], Product ID [0x5110], Addr [I2C0 0x50]

MMC: FSL_SDHC: 0, FSL_SDHC: 1

Loading Environment from MMC... *** Warning - bad CRC, using default environment

Failed (-5)

No panel detected: default to HDMI

Display: HDMI (1280x720)

In: serial

Out: serial

Err: serial

BuildInfo:

- ATF

- U-Boot 2018.03-svn73

switch to partitions #0, OK

mmc0(part 0) is current device

flash target is MMC:0

Net:

Error: ethernet@30be0000 address not set.

No ethernet found.

Fastboot: Normal

Uboot Version used:8.0

Normal Boot

Hit any key to stop autoboot: 0

magik2=>

magik2=> boot

switch to partitions #0, OK

mmc0(part 0) is current device

** Unable to read file boot.scr **

22481408 bytes read in 271 ms (79.1 MiB/s)

Booting from mmc ...

44939 bytes read in 10 ms (4.3 MiB/s)

## Flattened Device Tree blob at 43000000

Booting using the fdt blob at 0x43000000

Using Device Tree in place at 0000000043000000, end 000000004300df8a

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.14.98+g5d6cbea (sirisha@sirisha-Vostro-3800) (gcc version 7.3.0 (GCC)) #1 SMP PREEMPT Wed Jul 31 16:14:27 IST 2019

[ 0.000000] Boot CPU: AArch64 Processor [410fd034]

[ 0.000000] Machine model: Freescale i.MX8MQ MAGIK2

[ 0.000000] earlycon: ec_imx6q0 at MMIO 0x0000000030860000 (options '115200')

[ 0.000000] bootconsole [ec_imx6q0] enabled

[ 0.000000] efi: Getting EFI parameters from FDT:

[ 0.000000] efi: UEFI not found.

[ 0.000000] Reserved memory: created CMA memory pool at 0x0000000044000000, size 960 MiB

[ 0.000000] OF: reserved mem: initialized node linux,cma, compatible id shared-dma-pool

[ 0.000000] NUMA: No NUMA configuration found

[ 0.000000] NUMA: Faking a node at [mem 0x0000000000000000-0x000000013fffffff]

[ 0.000000] NUMA: NODE_DATA [mem 0x13ffbd180-0x13ffbef7f]

[ 0.000000] Zone ranges:

[ 0.000000] DMA [mem 0x0000000040000000-0x00000000ffffffff]

[ 0.000000] Normal [mem 0x0000000100000000-0x000000013fffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040000000-0x00000000b7ffffff]

[ 0.000000] node 0: [mem 0x00000000b8400000-0x000000013fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040000000-0x000000013fffffff]

[ 0.000000] psci: probing for conduit method from DT.

[ 0.000000] psci: PSCIv1.1 detected in firmware.

[ 0.000000] psci: Using standard PSCI v0.2 function IDs

[ 0.000000] psci: MIGRATE_INFO_TYPE not supported.

[ 0.000000] psci: SMC Calling Convention v1.1

[ 0.000000] percpu: Embedded 24 pages/cpu @ffff8000fff58000 s57624 r8192 d32488 u98304

[ 0.000000] Detected VIPT I-cache on CPU0

[ 0.000000] CPU features: enabling workaround for ARM erratum 845719

[ 0.000000] Speculative Store Bypass Disable mitigation not required

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 1031168

[ 0.000000] Policy zone: Normal

[ 0.000000] Kernel command line: console=ttymxc0,115200 earlycon=ec_imx6q,0x30860000,115200 root=/dev/mmcblk0p2 rootwait rw

[ 0.000000] PID hash table entries: 4096 (order: 3, 32768 bytes)

[ 0.000000] software IO TLB: mapped [mem 0xfbfff000-0xfffff000] (64MB)

[ 0.000000] Memory: 3052516K/4190208K available (12924K kernel code, 1794K rwdata, 5892K rodata, 1280K init, 429K bss, 154652K reserved, 983040K cma-reserved)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] modules : 0xffff000000000000 - 0xffff000008000000 ( 128 MB)

[ 0.000000] vmalloc : 0xffff000008000000 - 0xffff7dffbfff0000 (129022 GB)

[ 0.000000] .text : 0xffff000008080000 - 0xffff000008d20000 ( 12928 KB)

[ 0.000000] .rodata : 0xffff000008d20000 - 0xffff0000092f0000 ( 5952 KB)

[ 0.000000] .init : 0xffff0000092f0000 - 0xffff000009430000 ( 1280 KB)

[ 0.000000] .data : 0xffff000009430000 - 0xffff0000095f0a00 ( 1795 KB)

[ 0.000000] .bss : 0xffff0000095f0a00 - 0xffff00000965beb8 ( 430 KB)

[ 0.000000] fixed : 0xffff7dfffe7f9000 - 0xffff7dfffec00000 ( 4124 KB)

[ 0.000000] PCI I/O : 0xffff7dfffee00000 - 0xffff7dffffe00000 ( 16 MB)

[ 0.000000] vmemmap : 0xffff7e0000000000 - 0xffff800000000000 ( 2048 GB maximum)

[ 0.000000] 0xffff7e0000000000 - 0xffff7e0004000000 ( 64 MB actual)

[ 0.000000] memory : 0xffff800000000000 - 0xffff800100000000 ( 4096 MB)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=4, Nodes=1

[ 0.000000] Preemptible hierarchical RCU implementation.

[ 0.000000] RCU restricting CPUs from NR_CPUS=64 to nr_cpu_ids=4.

[ 0.000000] Tasks RCU enabled.

[ 0.000000] RCU: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=4

[ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0

[ 0.000000] GICv3: GIC: Using split EOI/Deactivate mode

[ 0.000000] GICv3: no VLPI support, no direct LPI support

[ 0.000000] ITS: No ITS available, not enabling LPIs

[ 0.000000] GICv3: CPU0: found redistributor 0 region 0:0x0000000038880000

<-- hang

-----------------------------------------------------------------------------------------------------

Regards,

Manoj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, PLL bypass mode. 200MHz and 50MHz PLL bypass mode is official supported in DDR script.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you help us why with 200MHz kernel hangs?

It hangs at this point of kernel code

clks[IMX8MQ_CLK_DRAM_ALT_ROOT] = imx_clk_fixed_factor("dram_alt_root", "dram_alt", 1,4);

drivers/clk/imx/clk-imx8mq.c funtion imx8mq_clocks_init().

but it works for 1600MHz and 800MHz.

Regards,

Manoj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you tell us which version of BSP are you using? And tell us your details steps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rita,

we are using imx-yocto-L4.14.98_2.0.0_ga

Using MX8M_LPDDR4_RPA_v24 we have configured for 200MHz clock and taken ds file.

then, using ds file calibrated the device and generated the lpddr4 timing file.

and in drivers/ddr/imx8m/lpddr4_init.c write 0x00EC6996 to the address 0x30360068(for 200MHz ddr frequency).

and it hangs in kernel imx8mq_clocks_init.

Regards,

Manoj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

https://community.nxp.com/docs/DOC-346061

DDR clock set you can refer to this

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manoj,

Are the 225MHZ DDR or DDR PLL frequency you are using?

Have a nice day

Best Regards

Rita