- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

I have a few technical questions regarding the M4 core of the i.MX6 solo X core

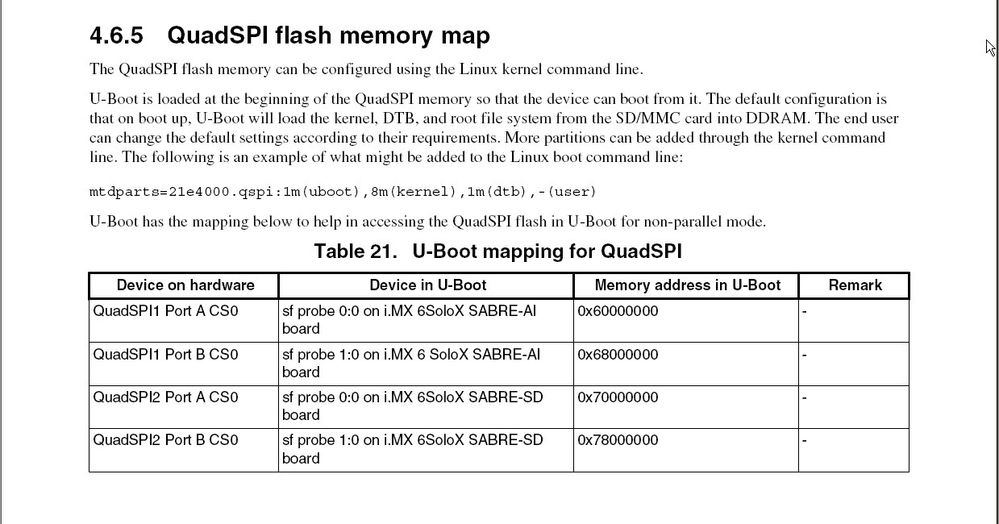

- I am working with the MQX 4.1.0 software for the solo X am trying to understand whyQSPI2 address 0x78000000 is used for the start of M4 core code (i.e. interrupt vector table). I am not seeing any explanation of this address determination in any of the Freescale documentation. Why is this starting halfway into the QSPI2 address space? Is this something specific to the actual SABRE-SD memory configuration? Please advise.

- I am also wondering why the MQX 4.1.0 software uses 4KB of memory at address 0x2091F000 for clock management share memory. According to Figure 8-3 in section 8.4.1 of the reference manual this memory is part of the 8K stack in OCRAM used by the system boot ROM. Is there a reason why this particular memory range was needed for this function? Could it be relocated? Is it considered acceptable because the U-boot is executing when this memory is overwritten?

- Can you please supply me with the source code for the U-boot image used to build the u-boot-sdb.imx image which is included in binary form only in the MQX 4.1.0 bundle?

已解决! 转到解答。

Hi Andrew

1. I.MX6SX addresses can be found in Table 2-1. System memory map IMX6SXRM

below part of i.MX_Linux_User's_Guide.pdf included in

2. Usage OCRAM as memory buffer is described in sect.3.2 Running the MQX RTOS on OCRAM

Application Note How to Run the MQX RTOS on Various RAM Memories for i.MX 6SoloX (Rev.1, 05/2015)

http://cache.freescale.com/files/microcontrollers/doc/app_note/AN5127.pdf

OCRAM usage is convenient in low power mode, when ddr is not available.

I do not think that Uboot overwrites this region.

3. please use linux sources L3.14.28_1.0.0_iMX6SX_BUNDLE

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Andrew

1. I.MX6SX addresses can be found in Table 2-1. System memory map IMX6SXRM

below part of i.MX_Linux_User's_Guide.pdf included in

2. Usage OCRAM as memory buffer is described in sect.3.2 Running the MQX RTOS on OCRAM

Application Note How to Run the MQX RTOS on Various RAM Memories for i.MX 6SoloX (Rev.1, 05/2015)

http://cache.freescale.com/files/microcontrollers/doc/app_note/AN5127.pdf

OCRAM usage is convenient in low power mode, when ddr is not available.

I do not think that Uboot overwrites this region.

3. please use linux sources L3.14.28_1.0.0_iMX6SX_BUNDLE

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

igor,

Thank you for this information.

However, I have follow-up questions.

1) Section 13.5 of the reference manual discusses the Cortex-M4 boot requirements. In particular it states that the A9-core is responsible for "...setting up Cortex-M4 initial exception table in TCRAML". The application note AN5127 that you referenced in your answer only specifies how to run the MQX code from QSPI (default from bundle), DDR, or OCRAM. There is no mention of how to execute code from TCRAML. This is possible right?

2) I tried to determine what address the A9-core would use to write to the TCRAML (prior to enabling the M4 core). Table 2-1 does not specify a System memory region for accessing the TCRAML from the A9 core. There is talk about a "backdoor" access port for the A9 to write to this memory, but no description on how to do so that I could find. All my attempts to try to write to this memory have failed (doing so from the U-boot command line prompt using the "cp" command). Please advise on the correct procedure.