- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: can imx6q support 4G DDR?

can imx6q support 4G DDR?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

can imx6q support 4G DDR?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi hui

yes, one can create service request to obtain i.MX6Q schematic with 4GB support.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear sir,

we now use 32-bit Android, it also can support 4G DDR?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

yes it can.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear dir,

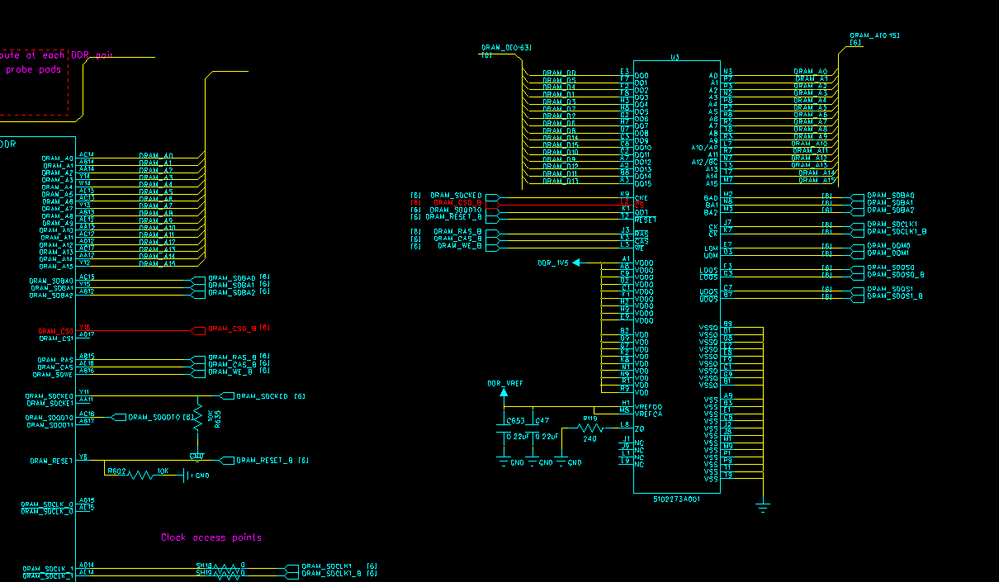

we now use only cs0 to connect four pcs DDR3(MT41K512M16 – 64 Meg x 16 x 8 banks),but only 2pcs(2G) is available.The method of connecting of one DDR3 refers to the picture below.

The question is how can I change to support the whole 4G memory,to change the shematic or replace another DDR3 ???

Thanks a lot !

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, hui wang:

I have the same problem with you: use only cs0 to connect 4 DDR3(MT41K512M16 64Meg x 8 x 8banks x 2 die),

and I succeeded in DDR Test, but the Uboot can not run with DDR_MB=4096.

However, if I set DDR_MB=3072 or DDR_MB=2048, it works successfully! Do you have solved problem?

Look forward to your reply, thanks!

Best regards!

Yujun

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yujun,

It sounds good that at least you succeed in DDR Test. Can you share your register programming values? Thank you very much!

Best regards,

Judy

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Judy:

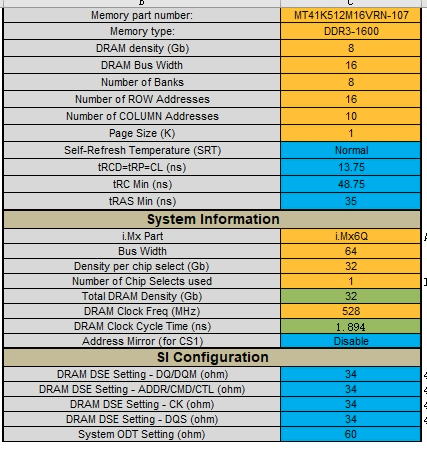

This is my configuration for your reference:

Best regards!

Yujun

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yujun,

I'm using the same 4GB DDR3 in i.MX6Q and I'm using the just one CS, CS0.

And I have some problem.

When I executed some application, Display was broken during the first 1~2 seconds.

I don't know what's the problem.

Could you share your DDR configuration file?

and could you review our situation?

You can see the same problem in the below link.

https://community.nxp.com/message/1143889

Best Regards,

Eric.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi!

I would prefer to have the full file instead of just the basic settings.

As you set the tRCD/tRP/CL to 13.75ns, this - divided by cycle time of 1.894ns and rounded - results in 8 cycles for your CAS Latency and 7 cycles for CWL, which JEDEC calls a DDR3-1066 8-8-8 setting.

Per JEDEC the tRCmin at that speed and CL setting is 52.5ns and the tRAS min is 37.5ns

But I think the DDR Register Excel tool sometimes makes some wrong calculations, thus please send me the full file.

Usually tFAW is also set incorrectly.

And I have some questions, for example if you were running the calibration or not. And how did you find the DRAM DSE settings?

I have sent you a private message.

Regards,

Thorsten

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yujun,

I am working with Junie on the issue and I think we are coming closer to get it solved. Some timings were incorrectly set, but still some fine tuning on the IOMUX SW PAD registers seems required as it still is not stable enough.

I would like to also help you as well to fix the timing registers. I have sent you a private message over this forum.

Regards,

Thorsten

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Thorsten:

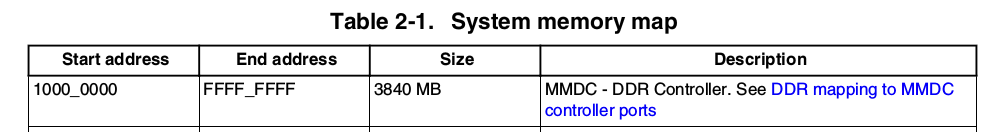

I have solved the problem, the max DDR size of i.MX6 is 3840MB:

It works ok when I set DDR_MB=3840 in uboot.

Best regards!

Yujun

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi hui wang:

一个cs0连接4片8Gb的DDR3是可行的吗?试验成功了吗?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Everyone,

Did you make it work? I also built a board with four pieces of 8Gb DDR3 (IM8G16D3FCBG-125) and imx6q. It has always failed in stress test (memtester). I wonder what can we do in Register values to make it work.

Has anyone tried Intelligent Memory 16Gb DD3? I am also very interested in knowing how it performs.

Thank you!

Judy

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have two customers running the 8Gb IM8G16D3FCBG on i.MX6 on their board. I will try to see if I can help you with a register dump from any of these two customers to verify where the issue is.

The 16Gb DDR3 is a future product from IM which is planned to be released in Q4

Regards,

Thorsten

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

i.MX6Q MMDC (MMDCx_MDCTL) supports memories with max. RAW=16, COL=12

so you can try to find appropriate memory.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Such 8Gb DDR3L with 16 Row and 12 Column Addressing is available from Micron and Intelligent Memory

Micron MT41K512M16HA-125

Intelligent Memory IM8G16D3FCBG-125

Intelligent Memory also offers them with industrial temperature range of -40 to 95°C Tcase.

Out of curiosity: Would anybody know if it's possible to bring the i.MX6 to 8GB RAM by using 4GB per each chip select?