- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: WDG_B must connect to system reset(POR_B reset) ?

WDG_B must connect to system reset(POR_B reset) ?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

WDG_B must connect to system reset(POR_B reset) ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Sir,

My customer question is why reboot command will cause WDG_B assertion and why CPU will hang if we do NOT connect WDG_B to system reset?

If we set reboot command in Linux 3.14, we can observe that imx6 watch dog WDG_B will assert.

If we do not connect WDG_B output to CPU POR_B reset input pin, then the CPU will hang , but We found Linux 3.0.35 is OK(not hang)

Does it mean the WDG_B “must” connect to system reset to reset whole system even if we do not need watchdog feature?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I found the same problem with you ?

And our board , the WDG_B does not connect to system reset POR_B

So,We found Linux 3.0.35 is OK(not hang), in linux 3.14.52 the CPU will hang ,

but in the uboot of 3.14.52 BSP, we can use reset successfuly.

Now , how to reboot CPU NOT with the pin WDG_B PIN ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

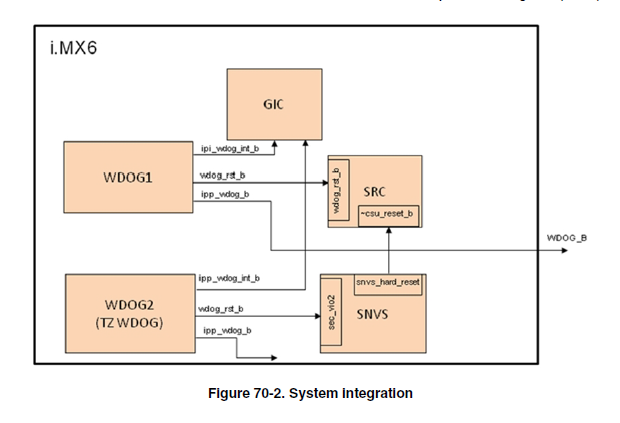

I would like to know which wdog is currently used? WDOG1 or WDOG2.

Currenty, the BSP L3.14.28 is using WDOG2, which is in the TZ.

And only way for WDOG2 without enable TZ is to toggle the WDOG_B for POR_B.

That is the i.MX6 SDB board hardware design.

But the WDOG1 is not in the TZ, the wdog_rst_b is connected to the SRC directly.

If you change the device tree to use wdog1, you will find differenct reboot reason in uboot.

Related the source code in the system.c which give chance to add the delay or the other operations before system can prepare to reboot. This depends on your system design.

So the BSP need to do some customization to system.c.

That is why you said in uboot reset is fine.

you need to stop something before reboot.

and the reboot in uboot is wdog reboot.

WDOG_B is better to give outsite a signal, the WDOG is to do reboot even using wdog1.

The typical use case is to reset the pmic to get the intialized status.

Next time, please report issue in detail, not just say hang someting, no any valuable information can help you to check issue.

POR_B reset by wdog2:

U-Boot 2014.04 (Mar 20 2015 - 23:29:57)

CPU: Freescale i.MX6Q rev1.2 at 792 MHz

CPU: Temperature 37 C, calibration data: 0x58e4f07d

Reset cause: POR

Board: MX6-SabreSD

I2C: ready

DRAM: 1 GiB

MMC: FSL_SDHC: 0, FSL_SDHC: 1, FSL_SDHC: 2

*** Warning - bad CRC, using default environment

No panel detected: default to Hannstar-XGA

Display: Hannstar-XGA (1024x768)

In: serial

Out: serial

Err: serial

Found PFUZE100 deviceid=10,revid=11

mmc1 is current device

Net: FEC [PRIME]

Normal Boot

Hit any key to stop autoboot: 0

WDOG reset by wdog1:

In Linux:

/unit_tests/memtool -16 0x20bc000=0x34

or modify the device tree to switch to use wdog1 and type reboot command line

imx6q-sabresd.dts

59 &gpc {

60 fsl,wdog-reset = <1>;

61 };

U-Boot 2014.04 (Mar 20 2015 - 23:29:57)

CPU: Freescale i.MX6Q rev1.2 at 792 MHz

CPU: Temperature 33 C, calibration data: 0x58e4f07d

Reset cause: WDOG

Board: MX6-SabreSD

I2C: ready

DRAM: 1 GiB

MMC: FSL_SDHC: 0, FSL_SDHC: 1, FSL_SDHC: 2

*** Warning - bad CRC, using default environment

No panel detected: default to Hannstar-XGA

Display: Hannstar-XGA (1024x768)

In: serial

Out: serial

Err: serial

Found PFUZE100 deviceid=10,revid=11

mmc1 is current device

Net: FEC [PRIME]

Normal Boot

Hit any key to stop autoboot: 0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Biyong,

Currently use 4.1.15 BSP, and surely using WDOG1, wdog1 can restart, but met hang issue in u-boot. I found that system.c mxc_restart doesn't make any sense because wdog driver register restart handler.

the hardware board using linux3.0.35 bsp, it is fine to reboot by wdog. can give some good advice? thanks.

=================================================================

U-Boot 2015.04-dirty (Dec 12 2017 - 17:29:37)

CPU: Freescale i.MX6D rev1.5 at 792 MHz

CPU: Temperature 38 C

Reset cause: WDOG

Board: MX6-SabreSD

I2C: ready

DRAM: 2 GiB

PMIC: PFUZE100 ID=0x10

imx6dqp not found!

incresase SW1AB/VGEN4 voltage!

incresase SW1AB/SW2/SW3AB/VGEN4 voltage!

MMC: FSL_SDHC: 0, FSL_SDHC: 1, FSL_SDHC: 2

No panel detected: default to Hannstar-XGA

Display: Hannstar-XGA (1024x768)

In: serial

Out: serial

Err: serial

flash target is MMC:2

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

if plug and unplug power adapter, it hasn't any issue(U-boot: reason cause: PORT).

hardware didnt use WDOG_B so that i can't trigger a POR reset. So are there some patch in 4.1.15 BSP that can trigger POR reset even if WDOG_B pin not used?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi JIMMY

for reliable reset wdog should reset whole board, as it is

done on Sabre schematic spf-27392 p.19, U507 p.21 with

signal PMIC PWRON.

CPU will hang if was reset from low power mode with lower

VDD_ARM, SOC voltages than needed for start-up.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------