- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: [Urgent] PCIe Clock Connection in i.MX6Q

[Urgent] PCIe Clock Connection in i.MX6Q

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all

Let me ask about the PCIe clock connection.

[Situation]

My customer want to debug with there custom board and MCIMX6Q-SDB.

So they need to make cable for connecting each other.

There custom board is as root complex and SDB is as end point.

[Question]

Q1.

I understand that it will transmit and receive data in a pair of TX and RX because the clock is encoded with 8b / 10b and the clock information is incorporated in the data.

So I think it's not required to connect CLKx_P/N which like a SDB.

Why does the CLK1_P/N connect to mini-PCIe connector in MCIMX6Q-SDB ? (Please see the SDB's schematic.)

Q2.

Clock pins of mPCIe are connected to CLK1_N (C7 pin) and CLK_P (D7 pin) of i.MX.

As a board I think that I am going to be RC, so this is an output pin. Am I correct ?

Q3.

Is it correct with understanding that there is no need to input a reference clock from i.MX externally when it becomes EP?

Q4.

On each board, each SoC has Refclock.

Is it correct in understanding that PCS TX / RX should be linked even if connected?

P.S.

I have already checked the following thread but I can't get the answer from it.

https://community.nxp.com/docs/DOC-95014

Ko-hey

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Ko-hey,

I confirmed your questions with PCIe driver designer, see following, please!

Q1.

Is it possible to communicate using MCIMX6Q-SDB in the case of "Using Internal Clock" ?

[A] Yes, it is. see above second conection.

Q2.

If yes, Is it enough to clear the Slot_Clock_Configuration bit in the PCIE_RC_LCSR register ?

[A] Slot_Clock_Configuration bit doesn't need to be set.

Have a great day,

Weidong

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi weidong.sun

I have two additional questions.

Q1.

Is it possible to communicate using MCIMX6Q-SDB in the case of "Using Internal Clock" ?

Q2.

If yes, Is it enough to clear the Slot_Clock_Configuration bit in the PCIE_RC_LCSR register ?

Ko-hey

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Ko-hey,

I confirmed your questions with PCIe driver designer, see following, please!

Q1.

Is it possible to communicate using MCIMX6Q-SDB in the case of "Using Internal Clock" ?

[A] Yes, it is. see above second conection.

Q2.

If yes, Is it enough to clear the Slot_Clock_Configuration bit in the PCIE_RC_LCSR register ?

[A] Slot_Clock_Configuration bit doesn't need to be set.

Have a great day,

Weidong

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for reply.

I'll talk with customer and contact you if I have additional question.

Ko-hey

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello ko-hey,

Q1: >>Why does the CLK1_P/N connect to mini-PCIe connector in MCIMX6Q-SDB ?

This is standard definitions for MiniPCIe, these 2 pins on connector is defined as PCIe Clock.

Q2: >>Clock pins of mPCIe are connected to CLK1_N (C7 pin) and CLK_P (D7 pin) of i.MX.

As a board I think that I am going to be RC, so this is an output pin. Am I correct ?

Yes, they are output pins, differential clock for external PCIe device.

Q3: >>Is it correct with understanding that there is no need to input a reference clock from i.MX externally when it becomes EP?

No. RC side should provide clock to EP device, so you should configure SabreSDB's PCIe to work at EP mode, and connect clock of RC side to CLK1_P/N pins of SabreSDB.

Q4: >>Is it correct in understanding that PCS TX / RX should be linked even if connected?

See Q3's answer.

in addtion, pay attention to connections of PCIe TX/RX between RC and EP.

RC_PCIe_TXP------>EP_PCIe_RXP

RC_PCIe_TXN------>EP_PCIe_RXN

RC_PCIe_RXP------>EP_PCIe_TXP

RC_PCIe_RXN------>EP_PCIe_TXN

Hope above suggestions will be helpful for you!

Best Regards,

Weidong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Weidong

> This is standard definitions for MiniPCIe, these 2 pins on connector is defined as PCIe Clock.

The standard is for Mini-PCIe to Mini-PCIe.

So if one side is PCIe, user don't have to provide and connect PCIe Clock.

Because the data of PCIe is including the clock data.

Is my understanding correct ?

> Yes, they are output pins, differential clock for external PCIe device.

Is it output pin if I configure the SDB as a EP ?

> No. RC side should provide clock to EP device, so you should configure SabreSDB's PCIe to work at EP mode, and connect clock of RC side to CLK1_P/N pins of SabreSDB.

I couldn't understand the reason.

In my understanding, PCIe don't need provide the clock to EP from RC when the reference clocks is provided to both RC and EP side.

Because the data of Tx/Rx include the clock data.

Specifically, the PCIe block of SDB has reference clock from an on-board oscillator.

So I think it don't need the reference clock to EP from RC via cable.

Could you tell me more detail about the reason why it needs the reference clock to EP from RC ?

Ko-hey

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Ko-hey,

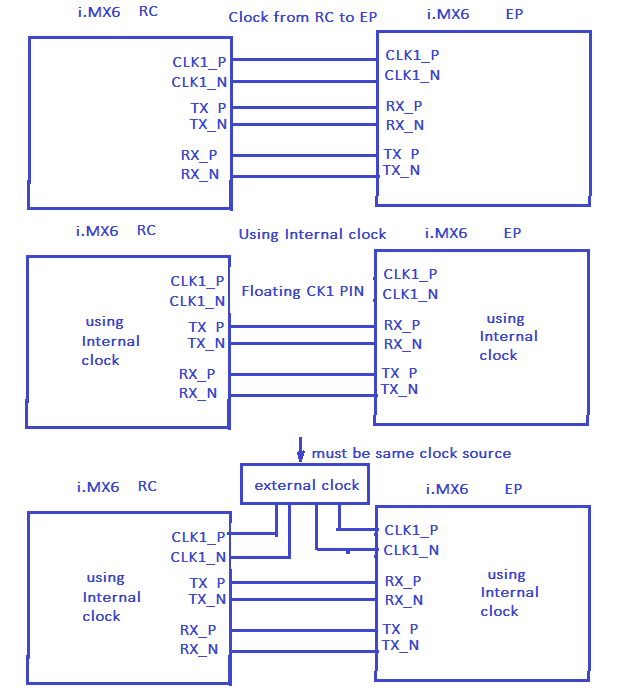

Probably I didnt' describe connections clearly, let do it again:

Actually , for you applications, you have 3 connections , see below:

For Second way: clock signal will be encoded into data stream.

Best Regards,

Weidong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Weidong-san,

I have a question same as Ko-hey-san, too.

Would you reply about a question of Ko-hey-san?

=======================================

I understand there're three clock architecture (connections) from you image.

Then, how can EP side detect the architecture ?

I can't find any registers to select the architecture.

Could you specify which i.MX6's register can select the architecture ?

Or could you tell me how to select the architecture in i.MX6 ?

======================================

Q1.

Is it possible to communicate using MCIMX6Q-SDB in the case of "Using Internal Clock" ?

Q2.

If yes, Is it enough to clear the Slot_Clock_Configuration bit in the PCIE_RC_LCSR register ?

======================================

Best Regards,

Yuuki

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Wingros Sun

I understand there're three clock architecture (connections) from you image.

Then, how can EP side detect the architecture ?

I can't find any registers to select the architecture.

Could you specify which i.MX6's register can select the architecture ?

Or could you tell me how to select the architecture in i.MX6 ?

Ko-hey

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Weidong

I have one more question.

I read PCI EXPRESS BASE SPECIFICATION, REV. 3.0 and found it has Slot Clock Configuration Bit.

The description for Slot Clock Configuration is as below.

---------------------------------------------------------------

This bit, when set, indicates that the component uses the same physical reference clock that the platform provides on the connector. If the component uses an

independent clock irrespective of the presence of a reference on the connector, this bit must be clear. For Root and Switch Downstream Ports, this bit, when set,

indicates that the Downstream Port is using the same reference clock as the Downstream component or the slot. For Switch and Bridge Upstream Ports, this bit

when set, indicates that the Upstream Port is using the same reference clock that the platform provides. Otherwise it is clear.

---------------------------------------------------------------

According to the description, it seems that I can select whether the reference clock is provided from connector (from RC) when I use the bit.

As a result, if I don't want to provide the clock from RC, I set the Slot_Clock_Configuration in the PCIE_RC_LCSR register.

Am I correct ?

Ko-hey