- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Shutting down cores on i.MX6D

Shutting down cores on i.MX6D

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My team and I are looking into the feasibility of shutting down one of the cores on our dual-core i.MX6 processor to reduce current consumption and thermal output.

I’ve been using the i.MX6DQ Reference Manual (Rev 2) as my main source of information. From searching through this document, it is my understanding that the two cores share the same clock (PLL1) and voltage rail (VDD_ARM_IN) and the only way to control their state is through the System Reset Control Register (SRC_SCR register 0x020D8000) shown in section 60.7.1. This register appears to have the ability to reset and enable/disable individual cores, expect for core0 which cannot be disabled. I don’t see anything else in the document related to disabling cores.

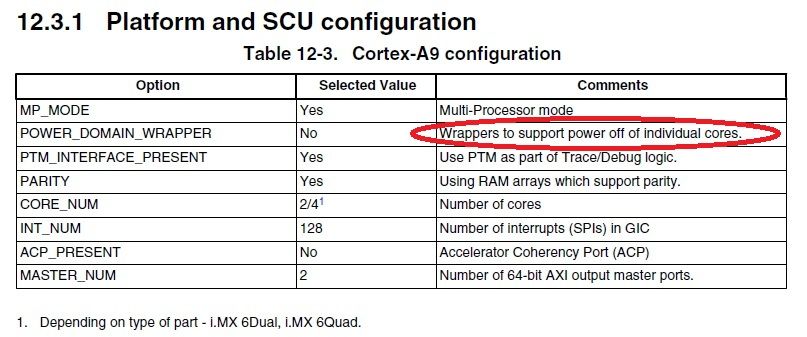

The OS we are using has an option to run on one or two cores. I have verified that changing this option in the OS changes the respective bit (bit 22: core1_enable) in the SRC_SCR register. I’ve also noticed little to no change in current when running on one core instead of two. The change in current was on the order of ~50 µA and which could have been caused by other variables in the system. In section 12.3.1, I see that the ‘POWER_DOMAIN_WRAPPER’ defined as ‘Wrappers to support power off of individual cores’ is not selected for the Cortex-A9 configuration. Does this mean that we cannot gate power to individual cores (i.e. cut power to the silicon of the second core)?

Unless I’m missing something, I’m inclined to think that disabling a core does not necessarily correspond to decreased current consumption and thermal output.

The questions my team has are:

- Is it possible to reduce current consumption and thermal output by disabling one of the cores in our dual-core i.MX6 processor?

- When a core is disabled on the i.MX6, what happens to that core?

- Is power to the core actually cut? Or is the silicon still powered, but just not executing instructions?

- Is enabling and disabling cores strictly done through the SRC_SCR Control Register (0x020D8000)?

- Or are there other registers and clocks that need to be gated for the second core to be ‘off’.

- Have you heard of customers shutting down cores to save power and/or reduce thermal output?

- If so, do you know of any documentation you could share with us?

- Do you have any other recommendations for power savings?

- Do you know of any CCM clocks that could be gated for significant power savings?

- I have Freescale’s AN4509 i.MX6 Power Consumption PDF that lists a few ideas for reducing power consumption.

Any input is appreciated!

Thank you,

Adam

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adam

1. yes

2. clock is not applied to core. Power may be cut for whole

Cortex-A9 Core Platform and this is described in sect.10.4.1.4.3.1 Cortex-A9

Core Platform, Power Gating Domain Management IMX6DQRM

3. yes

5. I believe one can also look at attached Linux Manual Chapters 16-20.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for the answers to Adam's initial post. They were very helpful! I have a few follow-up questions for you related to power management on the i.MX6:

- When an individual core is disabled through the SRC_SCR Control Register (0x020D8000), I see a reduction in dynamic power (when apps are running), but not static power (while in it's WAIT/idle state). Is this expected?

- This would seem to confirm that it is still powered, but not being clocked.

- You mentioned that power may be cut to the whole Cortex-A9 Core Platform which I believe cuts power to all of the cores in the cluster. Is it possible to cut power to any individual Cortex-A9 core within the cluster in the i.MX6?

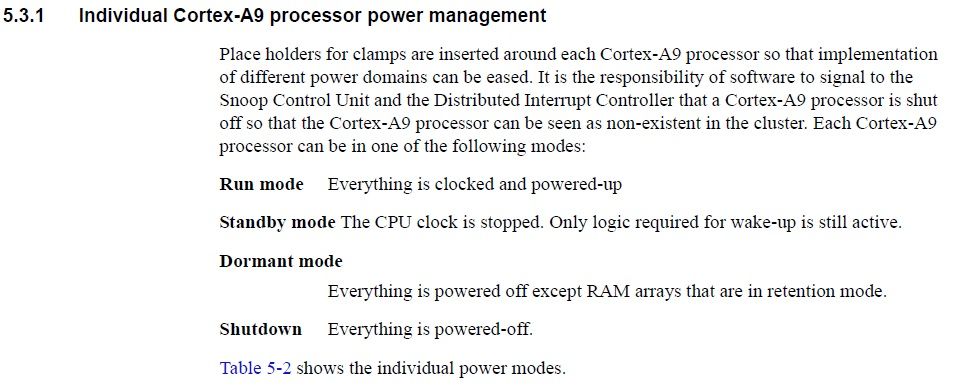

- I see in section 5.3.1 Individual Cortex-A9 processor power management of the Cortex-A9 MPCore Technical Reference Manual (DDI0407I_cortex_a9_mpcore_r4p1_trm.pdf) that ARM gives the option to implement different power domains for each processor.

- I also see in section 12.3.1 of the IMX6DQRM, that it appears Freescale did not implement the power domains which would provide the ability to power off individual cores on the i.MX6.

- This leads me to think that the answer to this question is a NO.

- If the answer to #2 is yes, is this done through the Snoop Control Unit (SCU)?

- Do you know of any documentation on how to do this for the i.MX6?

I have provided screenshots of the two sections referenced above for your convenience.

Thank you,

Scott

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott

as you correctly noted with reference to RM sect.12.3.1

power off individual cores is not supported by i.MX6.

>When an individual core is disabled through the SRC_SCR Control Register (0x020D8000),

>I see a reduction in dynamic power (when apps are running), but not static power (while in

>it's WAIT/idle state). Is this expected?

Yes.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for the information. Does Freescale have an estimate of how much static power is consumed by each individual core?

If it is significant (more than just a few mW), we may be forced to switch from an i.MX6 Dual to a Solo for our project.

Thank you,

Scott

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott;

Any updates on this? Have you figured out how to disable power to one of the cores?

I have already designed and developed using the Dual but would like to cut power further also.

Did you go with the Solo?

Thanks!

Brent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brent,

The terminology here appears to be key. Typically, when people hear 'shutting down a core', they tend to think of de-clocking it. Even though a core is de-clocked, it still draws static power and I have been unable to get an estimate of how much this is. This post specifically relates to cutting power to an individual core so it is consuming absolutely no power.

To answer your questions:

1) I don't believe you can disable power to an indivudual core due to Freescale's implementation of the power domains.

- Since each core has 4 voltage rails, I have considered physically disconnecting pins VDDARM_IN_5 through VDDARM_IN_8 to see what happens, but I have not been able to do so yet due to my board layout. I can't recommend doing this as I'm not completely sure what would happen. I believe in theory this would leave only Core_0 powered. But again, it's just an idea...

2) Since I am unable to get an estimate of static power consumption, I will likely have to populate a few boards with a Solo to answer my own question which will take time, money, and some SW modification.

Documentation worth looking at (in case you haven't yet):

1) AN4579: i.MX6 Thermal Management Guidelines http://cache.freescale.com/files/32bit/doc/app_note/AN4579.pdf

2) IMX6DQRM Section 10.4.2: Power Management Techniques

This processor can do a lot, but it will take both HW and SW to optimize it... something I am still working through.

I love to be proved wrong so if anyone has additional insight or recommendations, I'm all ears :smileyhappy:

Thanks,

Scott

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

put the maxcpus in the uboot. And it is linux common technology.

maxcpus=1 maxcpus=n : n >= 0 limits the kernel to

using 'n' processors. n=0 is a special

case. It is equivalent to "nosmp".