- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: RT1052 DMA P2M (LPUART to SDRAM)

RT1052 DMA P2M (LPUART to SDRAM)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT1052 DMA P2M (LPUART to SDRAM)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

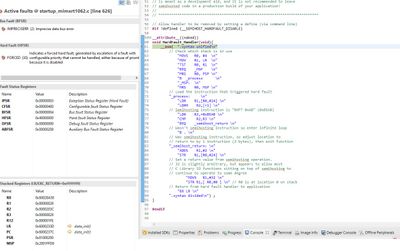

im searching for a solution concerning my problem with the DMA Transfer from LPUART to SDRAM.

Im using the FreeRTOS and LPUART + DMA. Actually the DMA transfers the incoming data from the UART to the Memory. Because o the space i switched the DMA Target to the configured SDRAM. After this i get issues. The first incoming data was successfully written to the SDRAM but after the first dma transfer to the sdram - the data wont change anymore in the sdram. But the incoming data from the uart is different to the data on the sdram.

What is the problem? Did anyone get this working ?(UART to SDRAM with DMA Operation?) Is there any Example?

SDRAM configuration:

status_t BOARD_InitSEMC(void)

{

printf("init SEMC\n");

semc_config_t config;

semc_sdram_config_t sdramconfig;

uint32_t clockFrq = EXAMPLE_SEMC_CLK_FREQ;

printf("SEMCclock %d\n",clockFrq);

/* Initializes the MAC configure structure to zero. */

memset(&config, 0, sizeof(semc_config_t));

memset(&sdramconfig, 0, sizeof(semc_sdram_config_t));

/* Initialize SEMC. */

SEMC_GetDefaultConfig(&config);

config.dqsMode = kSEMC_Loopbackdqspad; /* For more accurate timing. */

SEMC_Init(SEMC, &config);

/* Configure SDRAM. */

sdramconfig.csxPinMux = kSEMC_MUXCSX0;

sdramconfig.address = 0x80000000U;

sdramconfig.memsize_kbytes = 32 * 1024; /* 32MB = 32*1024*1KBytes*/

sdramconfig.portSize = kSEMC_PortSize16Bit;

sdramconfig.burstLen = kSEMC_Sdram_BurstLen8;

sdramconfig.columnAddrBitNum = kSEMC_SdramColunm_9bit;

sdramconfig.casLatency = kSEMC_LatencyThree;

sdramconfig.tPrecharge2Act_Ns = 18; /* Trp 18ns */

sdramconfig.tAct2ReadWrite_Ns = 18; /* Trcd 18ns */

sdramconfig.tRefreshRecovery_Ns = 67; /* Use the maximum of the (Trfc , Txsr). */

sdramconfig.tWriteRecovery_Ns = 12; /* 12ns */

sdramconfig.tCkeOff_Ns = 42; /* The minimum cycle of SDRAM CLK off state. CKE is off in self refresh at a minimum period tRAS.*/

sdramconfig.tAct2Prechage_Ns = 42; /* Tras 42ns */

sdramconfig.tSelfRefRecovery_Ns = 67;

sdramconfig.tRefresh2Refresh_Ns = 60;

sdramconfig.tAct2Act_Ns = 60;

sdramconfig.tPrescalePeriod_Ns = 160 * (1000000000 / clockFrq);

sdramconfig.refreshPeriod_nsPerRow = 64 * 1000000 / 8192; /* 64ms/8192 */

sdramconfig.refreshUrgThreshold = sdramconfig.refreshPeriod_nsPerRow;

sdramconfig.refreshBurstLen = 1;

return SEMC_ConfigureSDRAM(SEMC, kSEMC_SDRAM_CS0, &sdramconfig, clockFrq);

}

void Start_SEMC(void){

CLOCK_InitSysPfd(kCLOCK_Pfd2, 29);

/*163.86 MHz */

CLOCK_SetMux(kCLOCK_SemcMux, 1);

CLOCK_SetDiv(kCLOCK_SemcDiv, 1);

if (BOARD_InitSEMC() != kStatus_Success)

{

...

}else

...

}

DMA Config (rough):

DMAMUX_SetSource(EXAMPLE_LPUART_DMAMUX_BASEADDR, LPUART_TX_DMA_CHANNEL, LPUART_TX_DMA_REQUEST);

DMAMUX_SetSource(EXAMPLE_LPUART_DMAMUX_BASEADDR, LPUART_RX_DMA_CHANNEL, LPUART_RX_DMA_REQUEST);

DMAMUX_EnableChannel(EXAMPLE_LPUART_DMAMUX_BASEADDR, LPUART_TX_DMA_CHANNEL);

DMAMUX_EnableChannel(EXAMPLE_LPUART_DMAMUX_BASEADDR, LPUART_RX_DMA_CHANNEL);

NVIC_SetPriority(DMA0_DMA16_IRQn, 5);

NVIC_SetPriority(DMA1_DMA17_IRQn, 5);

/* Init the EDMA module */

EDMA_GetDefaultConfig(&config);

config.enableRoundRobinArbitration = true;

EDMA_Init(EXAMPLE_LPUART_DMA_BASEADDR, &config);

//#1 UART

EDMA_CreateHandle(&g_lpuartTxEdmaHandle, EXAMPLE_LPUART_DMA_BASEADDR, LPUART_TX_DMA_CHANNEL); //Handle for TX

EDMA_CreateHandle(&g_lpuartRxEdmaHandle, EXAMPLE_LPUART_DMA_BASEADDR, LPUART_RX_DMA_CHANNEL); //Handle for RX

//#UART1

LPUART_TransferCreateHandleEDMA(DEMO_LPUART, &g_lpuartEdmaHandle, LPUART1_UserCallback, NULL, &g_lpuartTxEdmaHandle,

&g_lpuartRxEdmaHandle);

The dma transfer worked for UART to normal mem. If i switch the location to:

receiveXfer.data = SomeAdressOfSDRAM

..i get the explained problem.

For a quick unsightly solution i let the dma write to normal mem and afterwarts i copy the data to SDRAM with memcpy. This is working fine - inside the callback function of the UART. But it is not the perfect solution for me.

Perhaps someone has a good example?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello jeremyzhou!

i have already tried some of the steps in the document.

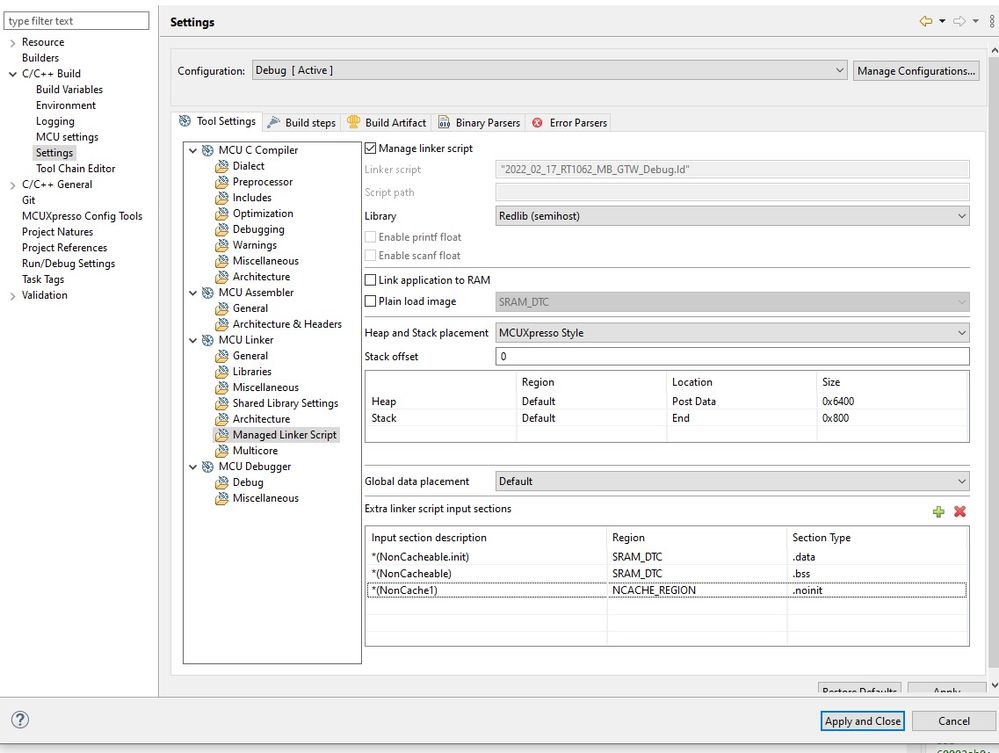

Can you please explain how to do the Step 2 (4.3.2. Use non-cacheable buffer -> 2. Linker file)

How can i implement it ?

Best regards

Felli

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

1) Can you please explain how to do the Step 2 (4.3.2. Use non-cacheable buffer -> 2. Linker file)

-- To provide the fastest possible support, I'd highly recommend you to refer to the linker file of the Hello World demo in the SDK library, as it supports an NCACHE region.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

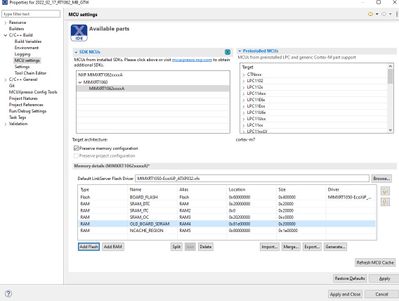

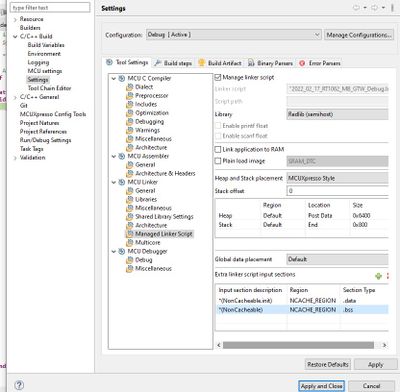

Here is my actual solution, this is working for me!

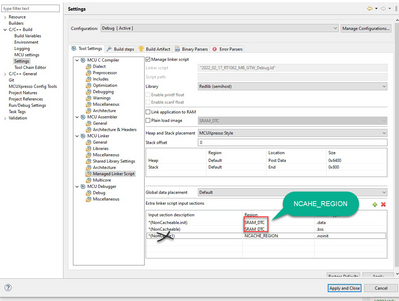

1. Linker Setings

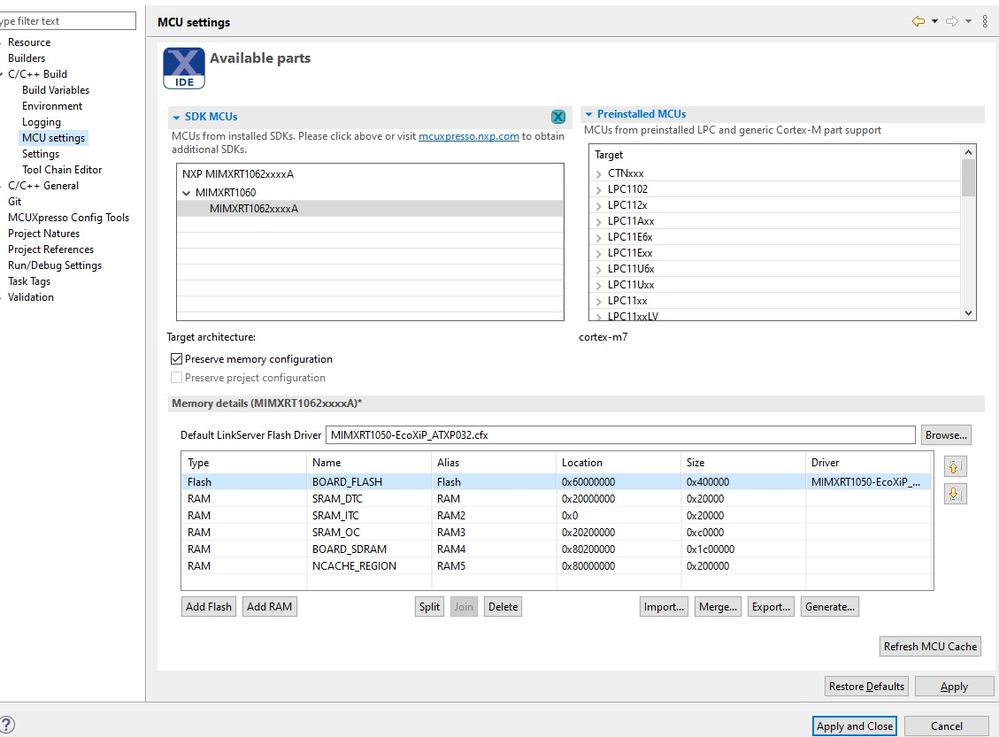

2. MCU Settings

I Think the solution was to define the SRAM DTC as BSS/DATA Section.

After that i choose just 2M for the NCHACHE REGION as first Step located at the beginning of SDRAM.

In my program i included the code part from the example out of the attached application node (3. MPU configurations).

Perhaps there is something to optimize @jeremyzhou ? otherwise the thread can be closed

Felli

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

It's unnecessary to create another region for NCACHE_REGION, you can use change the SRAM_DTC with the NCACHE_REGION.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

According to your reply, I guess the issue is related to the cache feature, as the cache brings a great performance boost, but the user must pay attention to the cache maintenance for data coherency, you can learn the details about it through the application note.

And you can upload the whole demo code for me to review.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------