- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Questions about iMX6 parallel display pixel clock limit

Questions about iMX6 parallel display pixel clock limit

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Questions about iMX6 parallel display pixel clock limit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have a customized imx6q(d) board. To the LCD interface, we found that the larger pixel clock is, more disorder the display will be. This will become obvious when pixel clock goes beyond 40Mhz.

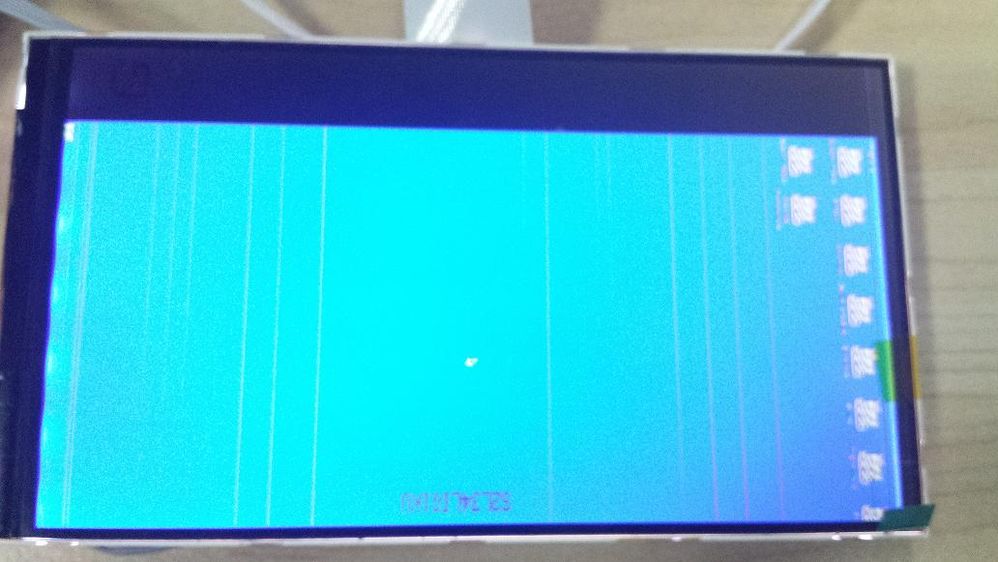

For an example, we try to attach a LCD to the parallel RGB port. The LCD parameters are 18bpp(rgb666), 720x1280, 60hz, pixel clock is about 57Mhz. According to the data sheet of the LCD, we set proper timing in the kernel source 'mxc_lcdif.c'. But the display seems to be messed enough.

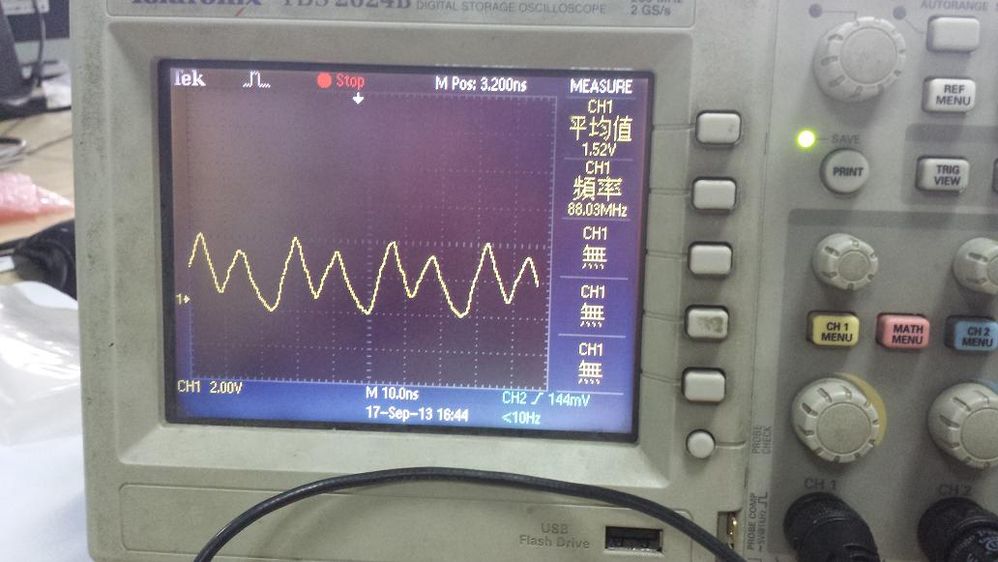

We captured the signal of the DI0_DISP_CLK (pixel clock of RGB signals), the waveform seems mess too.

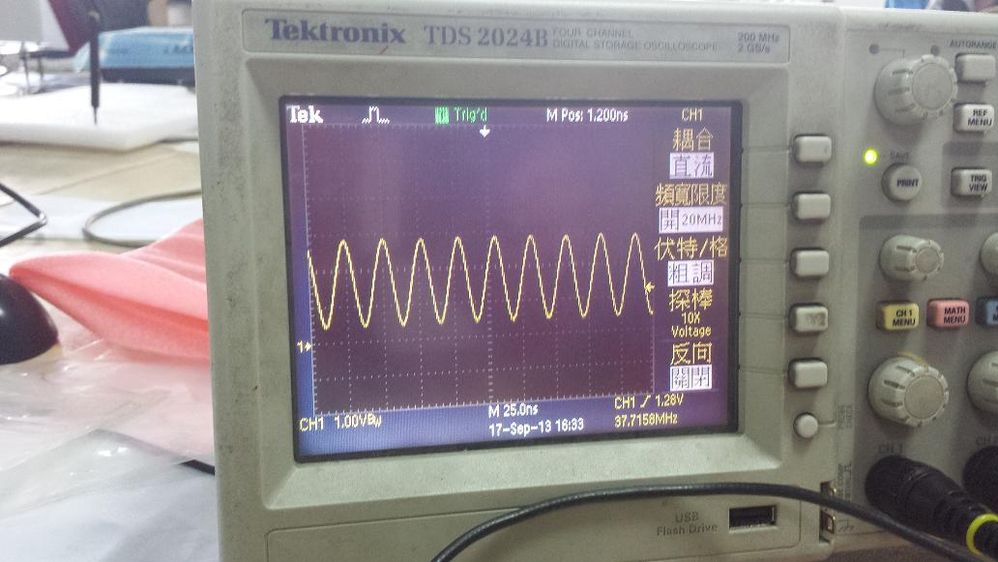

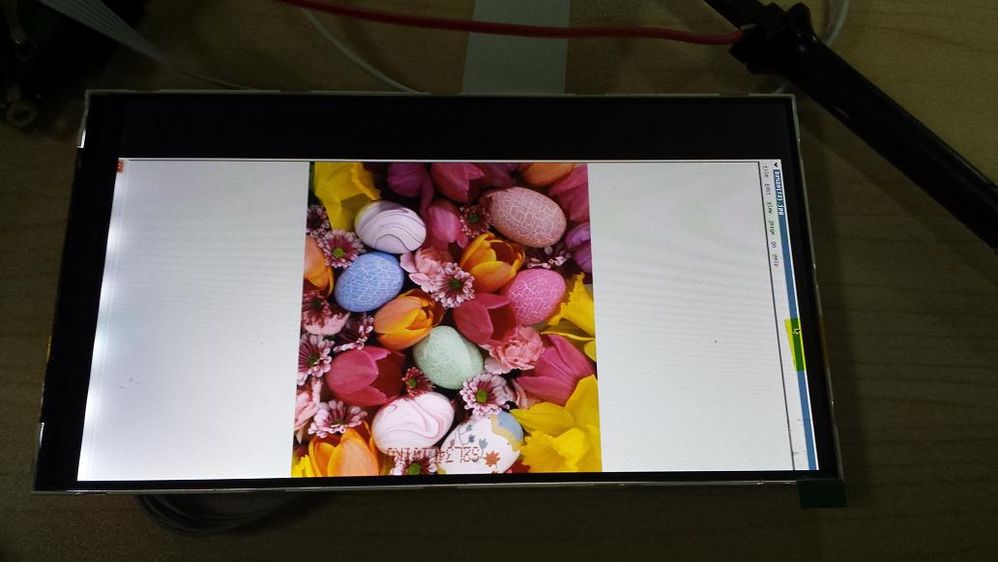

And then, we set the refresh frequency from 60hz to 30hz (in order to downgrade pixel clock without cropping image). Except the refresh frequency, none of the timing items are changed. Then, the display looks good.

We removed LCD from the port, and tried several RGB timing settings with different pixel clocks. Finally, we conclude the result mentioned at the beginning of article. We are using BSP package from 'L3.0.35_1.1.0_121218_source', with patch 03&04 applied. The waveforms of pixel clock are captured from the position most nearby the CPU.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Perhaps the problem relates to the fact, that output IPU pixel clock for LCD may have high jitter.

That's the expected behavior when the clock divider is set to a value that is not an integer.

Please look at IPU hardware parameters Tdicp and Tdpcp in the Datasheet(s).

When the divider is set to a non-integer value, the average frequency of the display clock will be

correct - but the clock will jitter. For applications that are sensitive to jitter, it may be recommended

to apply a clock ratio combination that allowed the clock divider to be set to an integer value.