- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

PF3000 PMIC questions, Dec. 2015

Thanks!

Some additional follow up questions:

- PF3000 standby:

- For driving this input signal, a N-channel MOSFET has been used (Q702). It seems that the reason for this circuitry is the note close to the MOSFET:

“ When PMIC_STBY_REQ pad is driving high state in SUSPEN mode, the output voltage level is about 2.0V. This voltage is lower than the 3.0V VDD_SNVS_IN supply voltage.”

I don’t understand this note. In i.MX6UL datasheet, section 4.6.2 Single Voltage General Purpose I/O (GPIO) DC Parameters, I can see that VOH is at least equal to OVDD-0.15. Since PMIC_STBY_REQ is supplied by VDD_SNVS_IN (3V), I would expect that PMIC_STBY_REQ is at least equal to 2.85V and not 2.0V. Where is this voltage coming from? Can I not use table 23 for calculating PMIC_STBY_REQ VOH level?

PF3000 standby VH level is at least equal to 0.8xVSNVS = 0.8*3V = 2.4V.

If my understanding is true, it would mean that no N-channel MOSFET is required and we could drive PF3000 STANDBY pin directly from i.MX6UL. Removing a MOSFET and some resistors on our module would be a nice news

[Winni] The analyses are perfect! But unfortunately, this is a bug of the processor, it is supposed to output 3.0V, however it is 2.0V when testing. So the MOSFET is necessary.

- i.MX6UL VDD_SNVS_IN supply input: (Extending the question below)

- i.MX6UL VDD_SNVS_IN supply input:

Why having a dual diode in front of VDD_SNVS_IN supply? Is it for avoiding backdrive through one of the sources (VDD_COIN_3V or VDD_SNVS_3V3)?

Is it possible to supply i.MX6UL VDD_SNVS_IN only with PF3000 VSNVS supply? Or is the diode required (D102) even if VDD_COIN_3V is not used? I understand the 1mA limitation of PF3000 SNVS supply.

[NXP] Yes, you are correct. The diode is for choosing one supply between VDD_SNVS_3V and VDD_COIN_3V.When COIN cell is empty, VDD_SNVS_3V3 could charge it via 1K R101; when VDD_SNVS_3V3 is absent, the diode can prevent the current from coin cell to VDD_SNVS_3V3. If no coin cell, the two diode can be removed and VDD_SNVS_3V can connect with IMX directly. However, it is recommend to keep the diode on the VDD_SNVS_3V3 if using PMIC VSNVS, since the PMIC VSNVS output is 3V, the VDD_HIGH_IN supply is 3.3V, these two pins were shorted within IMX processor, and so there will be a 0.3V voltage difference

[Digi] – Thanks a lot for your explanation !! This helps a lot.

Would it be possible then to leave i.MX6UL VDD_SNVS_IN unconnected (and powering it internally through VDD_HIGH_IN)? What would that mean in terms of components required on VDD_SNVS_IN and VDD_SNVS_CAP? Should we just keep the 220nF caps?

My understanding is that if we leave VDD_SNVS_IN unconnected, we would “just” lose the i.MX6UL RTC and SNVS (RTC) low power mode support. Right? One version of our product could definitively live with these limitations… On the second version, at least supporting SNVS (RTC) mode (and Tamper detection circuit) would be interesting… In this case, what would be the benefit of supplying VDD_SNVS_IN from the PF3000 VSNVS supply? In all power modes except SNVS (RTC), VDD_SNVS_IN would be supplied by VDD_HIGH_IN and no current would be drawn from the supply at VDD_SNVS_IN input. When i.MX6UL is in SNVS (RTC) mode, it means anyway that our system is supplied by a (very) low power supply – typically a coin cell. Then instead of having PF3000 generating VDD_SNVS_IN input supply, we could connect the coin cell directly there – and just have having the diode D103 in our system. We would not populate R101, since the coin cell would also be connected to PF3000 and this chip will be responsible for charging the coin cell. Would this combination work?

[Winni]I would like to know the intention for Digi not to follow the reference design, they want to save some components?

There is a problem of short 6UL VDD_HIGH_IN and VDD_SNVS_IN, in this case the VDD_HIGH_IN is supply by PF3000 LDO V33. V33 is not an always on regulator, that means there is no power of VDD_SNVS_IN domain/always on power supply when PF3000 off. In 6UL ref design, PF3000 PWRON pin is controlled by 6UL PMIC_ON_REQ which is VDD_SNVS_IN domain, this means the PWRON pin would never be pulled up/powered on. Of course you can pull up PWRON pin to PF3000 VSNVS directly, but if 6UL wants to shut up the system through pull PMIC_ON_REQ low, then the 6UL PMIC_ON_REQ pin would be out of control since no SNVS power supply, that may cause system reboot. If fact, I discussed this question with IMX team, they have never tried and tested the case that there is not an always on power supply for IMX processor, they do not guarantee there is no issue in real system operation.

Connect the coin cell directly to VDD_SNVS_IN, if the coin cell is not full, for example coin cell is 2.0V, it needs to wait PF3000 to charge coin cell into 3.0V firstly, then the system could power up.

I would recommend using PF3000 VSNVS to supply 6UL VDD_SNVS_IN via diode D102, removing the circuitry VDD_COIN_3V to 6UL VDD_SNVS_IN, and connect the coin cell with PMIC LICELL with 1K resister. PF3000 will switch coin cell to supply VDD_SNVS_3V3 internally when there is no main input.

Thank you for the answers, a few more questions from Digi:

- Concerning the reference design for 9x9 processor and PF3000, MCIMX6UL-9x9CM (document number SCH-28865), currently using revA1 of the document. Is this the latest one?

[b43723] Yes, rev A1 is the latest one.

- Why adding a delay on POR_B to i.MX6UL processor compared to PMIC? Delay circuitry: R511/R519/C503. Is it mandatory?

[b43723] This circuitry is reserved for adjust the sequencing, it is not mandatory but recommend to reserve it in case there is problem in future.

- i.MX6UL VDD_SNVS_IN supply input:

Why having a dual diode in front of VDD_SNVS_IN supply? Is it for avoiding backdrive through one of the sources (VDD_COIN_3V or VDD_SNVS_3V3)?

Is it possible to supply i.MX6UL VDD_SNVS_IN only with PF3000 VSNVS supply? Or is the diode required (D102) even if VDD_COIN_3V is not used? I understand the 1mA limitation of PF3000 SNVS supply.

[b43723] Yes, you are correct. The diode is for choosing one supply between VDD_SNVS_3V and VDD_COIN_3V.When COIN cell is empty, VDD_SNVS_3V3 could charge it via 1K R101; when VDD_SNVS_3V3 is absent, the diode can prevent the current from coin cell to VDD_SNVS_3V3. If no coin cell, the two diode can be removed and VDD_SNVS_3V can connect with IMX directly. However, it is recommend to keep the diode on the VDD_SNVS_3V3 if using PMIC VSNVS, since the PMIC VSNVS output is 3V, the VDD_HIGH_IN supply is 3.3V, these two pins were shorted within IMX processor, and so there will be a 0.3V voltage difference.

Thanks!

====================================================================================

I have a few questions concerning using PF3000 on our ConnectCore i.MX6UL module. See below:

- PF3000 - VREFDDR

- On MCIMX6UL-9x9CM revA1, this supply has a 1µF decoupling capacitor. The supply is only connected to R209 which is not populated. What does this mean? Should we not use this supply? If we don't, do we still need the 1µF cap?

[b43723] In the reference design, there a two ways to supply the VREFDDR, by PMIC and by discrete resisters. We recommend to use the PMIC VREFDDR since it can save components and current, in this case it needs to populate R209. However, there it a typo in schematic, the VINREFDDR is not connected to DRAM_1V2 and left floating, that’s why they updated the schematic and didn’t populate R209.

- PF3000 - VLPDDR2_1V2

- On MCIMX6UL-9x9CM revA1, VINREFDDR is connected VLPDDR2_1V2. However, this supply seems not to be present anywhere else. Is this an error? Where should this supply be connected?

[b43723] Yes, this is a mistake. It should be connected to DRAM_1V2.

- PF3000 - VDD_SNVS_3V3

- On MCIMX6UL-9x9CM revA1, PF3000 supply VSNVS has two decoupling caps (C738 and C739) and is connected then to a 0R resistor (R760) which is not populated. Instead of using PF3000 VSNVS supply, VDD_SNVS_3V3 is generated through an external LDO (U701 - RT9169-33GVL). Any reason why this is done in this way?

[b43723] In PF3000 off mode, the PMIC current capability is only 35uA, but there is a reset chip U708 needs to consume more than 100uA in off mode, so in some cases (VSYS<4.6V & no coin cell) the PF3000 could not power up. There are two workarounds for this issue, one way is to switch U708 supply from VDD_SNVS_3V3 to board 5V input VSYS, another way is to use an external LDO.

====================================================================================

- Inductors for DC/DC converters:

I have seen that you suggested in the datasheet of PF3000 following inductors for the buck regulators:

- TAIYO YUDEN BRL3225T1R5M

- TOKO DFE201610E-1R5M

- Question 1: Why is TAIYO YUDEN BRL3225T1R5M marked as "alternate for low power applications". Because its rated current is lower: 2.2A vs 2.9A?

Correct. The Tayo inductor is an alternate inductor for low power applications. For cost reduction, I picked the same inductors for all bucks. I calculated the max saturation current needed for the worst case on SW1B (-30% derating on 1.5uH inductor, 4.5V VIN, 1.425V VOUT). That gives an inductor ripple of 460mA, added a 50% safety margin on it, added the rated DC current of 1.75A: this gives max sat current of 2.45A. This is for applications running @ rated switcher current. For low power application, the DC current will be lower, that is why I picked a lower saturation current.

See attached my calculation spreadsheet that you can use internally for fine tuning.

- Question 2: Would TDK VLS201612CX-1R5M or TDK VLS201612HBX-1R5M-1 be good alternatives for an i.MX6UL design?

Their max saturation current when inductance decreases by 30% is 1.62A. That could be fine for SW1A and SW2. Probably too low for SW3 and SW1B.

Toko is 2.9A for the same size, see attached spec (check with Murata directly for samples and price).

As you can see, it really depends on the final application. You will have to make a trade-off with performance, cost and size.

- Question 3: Would 1µH inductors be an option here? We are using 1µH inductors on ConnectCore 6. Reusing them here would help to increase our volume and decrease our BOM costs. We are using TAIYO YUDEN MAKK2016T1R0M (2.2A) and TOKO 1239AS-H-1R0M (3A) models.

[b43723] Q1: there always some margin between the DCDC max output current and inductor rated current.

Q2: the rated current for TDK VLS201612CX-1R5M is 1.8A and TDK VLS201612HBX-1R5M-1 is 2.5A.

Q3: with 1.5µH inductor, the PF3000 DCDCs can get good phase margin.

For the above three questions, I’d like to invite Adrien and Sean to confirm…

To keep circuit stability, you will have to keep the L.C product equal. Which means re-calculate the output capacitance.

- 1.5uH x 44 uF = 66.10e-12

C=66uF=3x22uF

So you can use a 1.0uH inductor if you add an additional 22uF output capacitor.

Note that using a lower inductor value will:

- Increase current ripple

- Increase output voltage ripple (at constant C)

- Improve transient response

- improve efficiency at heavy load (if lower DCR)

- reduce efficiency at light load

Try to keep inductor ripple current equal to 20 – 40 % of DC current.

Increasing output capacitance will:

- Reduce output voltage ripple

- Increase response time during load transients

- PF3000 and i.MX6UL (9x9mm):

- When using i.MX6UL processor in 9x9mm package and PF3000 PMIC, which is the best reference board I should look at? Is it MCIMX6UL-9x9CM (document number SCH-28865)? This document is only available on the extranet. Is this an official reference board tested?

[b43723] Yes, sch-28865 is the recommended one for the i.MX6UL processor in 9x9mm and PF3000. In fact, this solution is fully validated by IMX team, and the customer can get official reference design, BSP and the technical support.

Additionally power supply decoupling questions:

Document called “Hardware Development Guide for the i.MX6UltraLite Applications Processor” (IMX6ULHDG) and table 9 shown below is providing very precise placement information for the decoupling capacitors. The data below are for the 14x14mm package. We are using the 9x9mm one. Would you have similar information for this package?

[b43723] I checked with IMX HW AE, the requirements of the decoupling caps for the 14x14 and the 9x9 processor are the same, so the values here are the same, they will update this the next time.

Hi Massimo,

If you have 3.8V directly supply to PF3000 VIN pin, in this case, the Front-End LDO regulator is not used : the external MOSFET has to be unpopulated and VPWR pin must be connected to GND. The capacitors on VPWR can be removed and only a 2.2uF capacitor on VIN to ground is necessary in this case.

Thanks.

Sean

Hi,

I have used Freescale schematic to draw circuit for i.MX6UL and PF3000. However I am facing issue that VIN voltage is 4.21V (Should be between 4.3V to 4.5V as per datasheet). We are getting pull up of 2.2V at PWRON pin with supply VDD_SNVS_3V3. (As per datasheet, should be atleast 2.4V as VH = 0.8 X SNVS = 0.8 X 3 = 2.4V).

I am not able to understand if the PMIC is in PWR Off mode (because of 2.2V pull up). PWRON pin is also driven by CPU which is mounted but not powered (is the loading of 2.2V on PWRON pin is happening because of this?).

I also have provision of external LDO for VDD_SNVS_3V3 generation, which I have not assembled.

Now with 4.21V of VIN, I am getting all the power rails output voltage as expected from datasheet, but when I am loading the rails individually with 100mA current, the voltage is falling down on all rails (except VDD_SNVS_3V3 which is standstill 3V).

Could you please guide me at the earliest.

Regards,

Surendra

Hi NXP,

about the question-1 answer "[Winni] The analyses are perfect! But unfortunately, this is a bug of the processor, it is supposed to output 3.0V, however it is 2.0V when testing. So the MOSFET is necessary." Do you plan to solve it by revising chip? Or it's already solved.

BRs

Mark

Hi Mark,

It was fixed. See the ERR009454 in the document the Chip Errata for the i.MX 6UltraLite IMX6ULCE Rev.1, 04-2016 click the link: http://www.nxp.com/assets/documents/data/en/errata/IMX6ULCE.pdf?fsrch=1&sr=1&pageNum=1

Regards,

Sean

NXP PMIC team

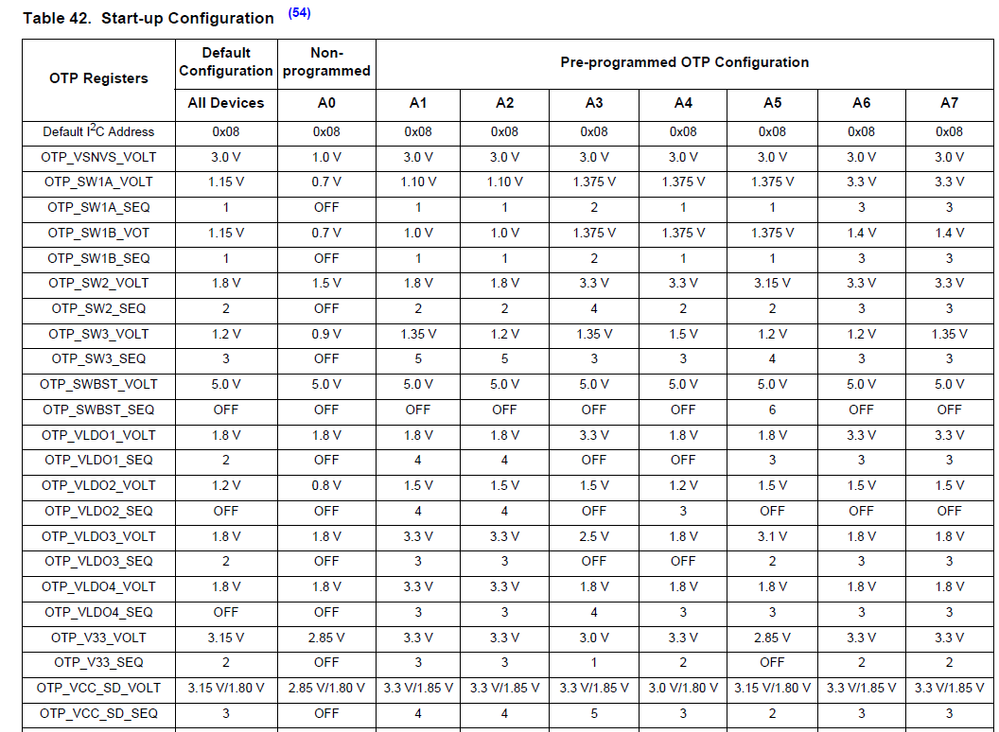

Additional question regarding configuration of the PF3000

For i.MX6UL, only two configurations are valid: A6 and A7. A6 is made for LP-DDR2 whereas A7 is made for DDR3L.

In our design, we are using VLDO3 for supplying NAND flash with 3.3V. By default, the voltage on this supply is 1.8V.

- 1. Is it possible to order customized start-up configuration directly from the factory? Or do you see another way to change the default voltage of LDO3?

- 2. On the other side, with the setting of SW3, only DDR3L are supported and not standard DDR3. I assume that other customers have requested support for 1.5V DDR3 chip. How could we manage this?

Hi Samuel,

I would recommend you to contact the Marketing team if you need a custom programmed PF3000 from the factory.

I'm sending you an email with more details about your questions.

Have a great day,

Jose

An additional question:

PF3000 – Pads VPWR, LDOG and VIN will be routed to our

module pads (LGA module). Knowing this, the power MOSFET normally connected to

these signals when running PF3000 at 5V will be on the carrier board. Is this

acceptable? What are the recommendations in terms of spacing between

VPWR/LDOG/VIN and the MOSFET? Should we plan any component close to these pins

(capacitors)? Need these pins support high current?

Hi Samuel,

There should not be any problem by having the 5V signal on the carrier board, unfortunately we do not have specific recommendation in terms of spacing between VPWR/LDOG/VIN and the MOSFET, but I do not think that this could be an issue, although it is recommended that Power components should be all placed on the same side of board and their power traces routed on the same layer, in order to reduce voltage drop.

If it is necessary to route a power trace to another layer, choose a trace in low di/dt paths and use multiple vias for interconnection.

There are other recommendations in terms of place components closed to the PMIC, place these components as close as possible to the IC in order of priority:

- Input capacitor of the buck regulators (SW1A, SW1B, SW2, and SW3)

- Output diode and output capacitor of the boost converter (SWBST)

- VIN, VCOREREF, VCORE, and VCOREDIG capacitors

- LICELL capacitor (if a coin cell is used in system)

- VSNVS, VREFDDR, and linear regulators capacitors (VLDOx, VCC_SD and V33)

- Switching regulator inductors

You can find more layout recommendations for the PF3000 in the application note AN5094

Have a great day,

Jose

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------