- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- MMDC chip select in DDR3 with i.MX6DL

MMDC chip select in DDR3 with i.MX6DL

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all

My customer plan to use DDR3 and want to divide DDR memory by function.

For example, one is for boot and the other is for image buffering.

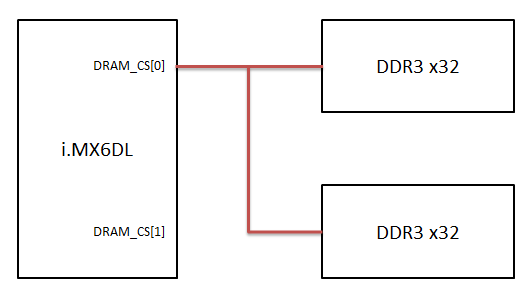

SABRE-SDP is following connection. (Figure 1)

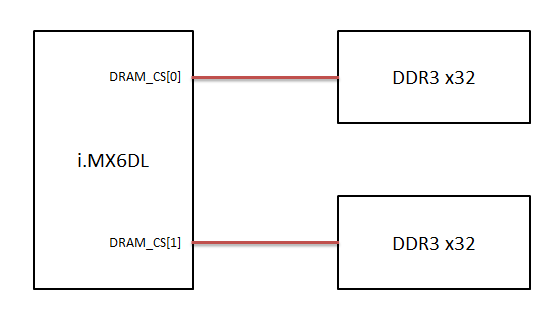

My customer wanto to use following connection. (Figure 2)

However, according to the Table 45-13 of IMX6SDLRM Rev. 2, 04/2015, MMDC support 2 channels only when user use LPDDR2.

Q1

Can we use like Figure 2 ?

Q2

If Q1 is yes, can we divide DDR memory by function ?

For example, one is for boot and the other is for image buffering.

Ko-hey

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Ko-Hey,

You may use one Chip Select for both DDR chips, or one Chip Select for each DDR chip. Both figures presented are valid configurations. However, when using two Chip Selects the memories are mapped as a bigger combined memory, not as two separated memories.

I’m not familiar with implementations that use the configuration you mention, using a DDR chip for booting and system memory and another DDR chip dedicated to image buffering. You may use a dedicated memory location on your implementation though, which would be the closest to using each chip for a dedicated purpose.

I hope this information helps!

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Ko-Hey,

You may use one Chip Select for both DDR chips, or one Chip Select for each DDR chip. Both figures presented are valid configurations. However, when using two Chip Selects the memories are mapped as a bigger combined memory, not as two separated memories.

I’m not familiar with implementations that use the configuration you mention, using a DDR chip for booting and system memory and another DDR chip dedicated to image buffering. You may use a dedicated memory location on your implementation though, which would be the closest to using each chip for a dedicated purpose.

I hope this information helps!

Regards,