- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IMX8MQ to IMX8MQ communication using PCIe cross-link

IMX8MQ to IMX8MQ communication using PCIe cross-link

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMX8MQ to IMX8MQ communication using PCIe cross-link

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP Team,

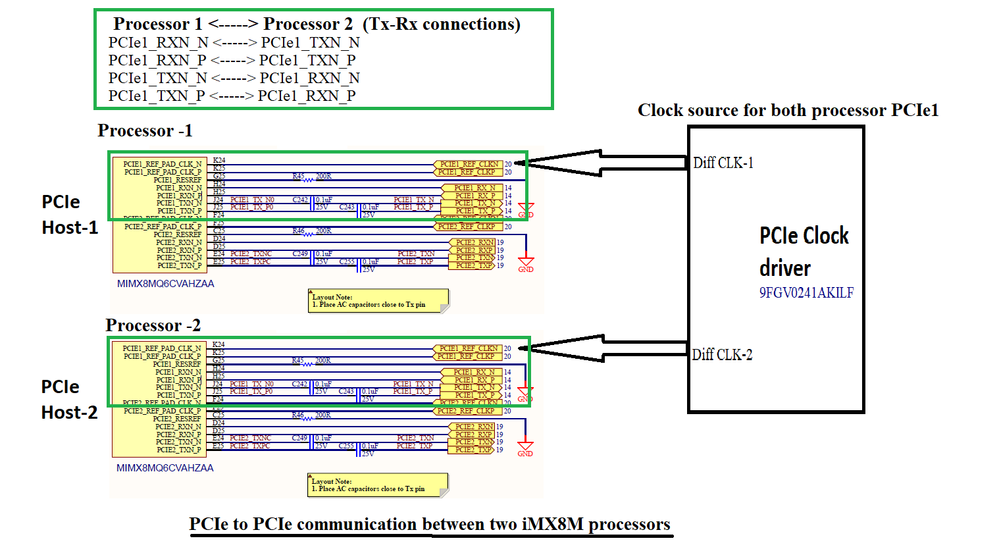

In one of the hardware designs we are planning to establish a communication link between two IMX8MQ processors. For that we are planning to use the PCIe as the communication medium. The reason we are trying to establish a connection using PCIe is to save the PHY space in the circuit.

On the hardware front, we are planning to establish communication using as per the below diagram.

- Can you please help to verify the hardware connections and check whether this design is feasible or not from the standard point of view?

- Can we get some software reference for this method? (I have already searched the queries in this forum but not able to find the same?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harshit

yes this design is feasible, also one can look at below link

(as pcie module is similar to i.MX6)

i.MX6Q PCIe EP/RC Validation System

For software use linux pcie driver described on

i.MX Software and Development Tools | NXP

or baremetal sdk (1.1.0_iMX6_Platform_SDK.zip) on link SMP Enable in IMX6

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi igorpadykov,

Thank you for your reply and confirmation of the hardware connections.

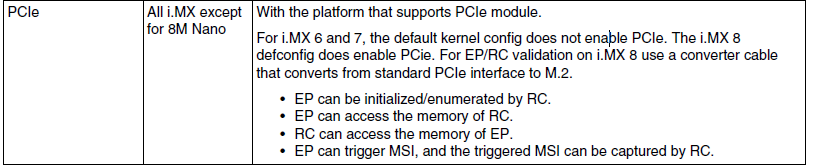

We are planning to use the Linux reference here. From the Linux release notes manual I verified that the EP and RC mode support is there in i.MX8MQ processor.

- From the link, you have shared in the above reply specifies that the external clock is not required, we can go with the internal PCIe clock in EP. Please confirm.

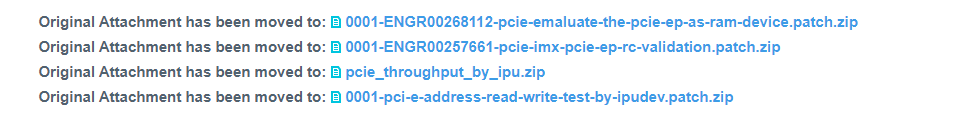

- In the previous link we got the following information. However, we are not able to access those files. Can you please provide us the same?

- In our end application we want to establish full-duplex communication between two processors. (which might not be the video data). How we can build the same?

- In the application how we can establish the synchronization between these two reads and write? Is this something already implemented by NXP?

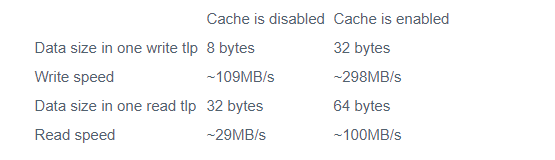

- Will we get a similar throughput on imx8Q as well as mentioned for imx6Q?

- With the above connections whether the throughput will be more if we use RGMII interface (instead of PCIe) for communication between two processors?

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harshit

1, yes in this case internal PCIe clock can be used.

For other questions please create new threads.

Best regards

igor