- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

IMX6ULL CSI Control Register

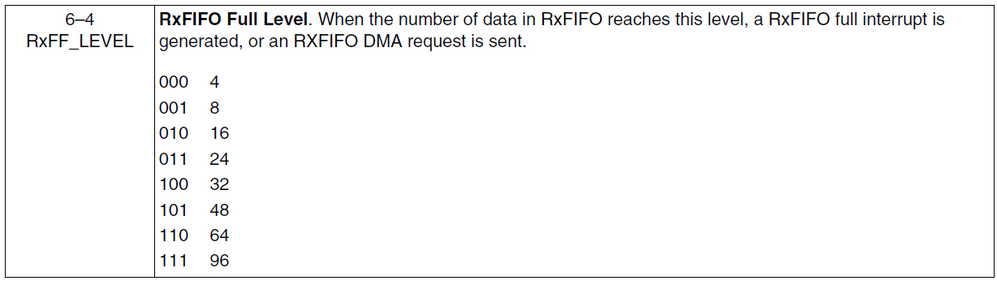

1. The CSI module has the 256 x 64 RxFIFO to store received image pixel data at the speed of the image sensor pixel clock. When the number of remaining empty slots in the RxFIFO reaches the level, specified by the RxFF_LEVEL bits, the interrupt or DMA request is generated and the software or the CSI DMA engine flushes the RxFIFO content to the framebuffer area, located in the main system memory.

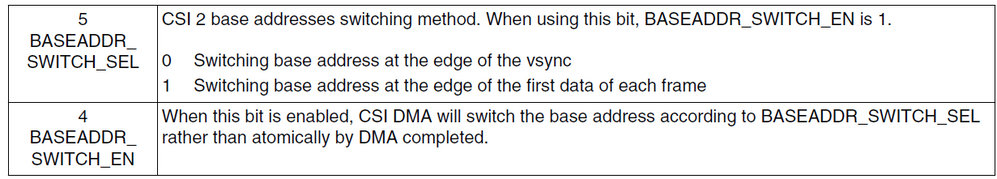

2. The CSI module supports so-called double buffer mode, in which it can store two consecutive frames into different frame buffers to simplify further frame processing in software. In case of DMA transfer, the CSI DMA engine switches the base address of the frame buffers after completing the frame transfer. Typical mechanism is that DMA does it automatically immediately after completing a frame transfer. There are two alternate methods of switching the base address: when receiving the next VSYNC edge and when receiving the first data of the next frame to RxFIFO. So, the BASEADDR_SWITCH_EN bit enables these alternate methods, and the BASEADDR_SWITCH_SEL bit selects between them.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Artur Petikhov,

Thanks for your help.

And I have a others question,

I am trying to use one camera(output 720*240 interlace) connect to the IMX6ULL board.

And I set CSICR1 bit 27 VIDEO_MODE to interlace mode and CSICR18 bit 2 DEINTERLACE_

EN to deinterlace enabled but doesn't work.

Do you know why?