- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: How to add a new NAND Flash support in iMX31 WinCE5.0 BSP,which files i need to modify ?

How to add a new NAND Flash support in iMX31 WinCE5.0 BSP,which files i need to modify ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Everyone,

Currently,I have a WinCE5.0 imx31 Board need to change nandflash from SamSung K9F2G08U0CSCB to Skynix H27U4G8F2DTR. I modify the K9F2G08U0A.h the .h file of SamSung K9F2G08U0CSCB in my project E:\WINCE500\PLATFORM\JS313\Src\Common\Nandfmd directory like

#define NAND_BLOCK_CNT (4096) //Samsung 2048 //Skynix 4096

#define NAND_MAKER_CODE 0xad // Samsung ec // Skynix AD

#define NAND_DEVICE_CODE 0xdc //da //DC

But my board cant boot normally . This is the log

///////////////////////////////////////////////////////The log of H27U4G8F2DTR////////////////////////////////////////////////

INFO: Using device name: 'MX3121862'

INFO: Reading NK image to NAND (please wait)...

INFO: Copying NK image to RAM address 0xA8100000

INFO: Load is 100% complete.

INFO: Copy of NK completed successfully.

Download successful! Jumping to image at 0x0@(physical 0x80100000)...INFO:OALLogSetZones: g_oalLogMask: 0xb

INFO: PBC Version = 0x0

Windows CE Kernel for ARM (Thumb Enabled) Built on Jun 24 2004 at 18:25:00

ProcessorType=0b36 Revision=4

sp_abt=ffff5000 sp_irq=ffff2800 sp_undef=ffffc800 OEMAddressTable = 88101584

OEMInit: SREV = 0x29

PBC debug switch settings: 0x0

SSI1 clock frequency: pBSPArgs->clockFreq[DDK_CLOCK_SIGNAL_SSI1] = 1719900 Hz

SSI1 clock frequency: mcuPllFreq = 532000000 Hz

SSI1 clock frequency: BSP_CLK_USBPLL_FREQ = 240000000 Hz

SSI1 clock frequency: BSP_CLK_SERPLL_FREQ = 220147200 Hz

SSI1 clock frequency: div = 128

BSP System Configuration:

L2 CACHE ENABLED

MCU PLL = 532000000 Hz

USB PLL = 240000000 Hz

SER PLL = 220147200 Hz

ARM CLOCK = 266000000 Hz

IPU CLOCK = 133000000 Hz

AHB CLOCK = 133000000 Hz

IPG CLOCK = 66500000 Hz

NFC CLOCK = 26600000 Hz

GACC CLOCK = 66500000 Hz

PER CLOCK = 66500000 Hz

SSI1 CLOCK = 1719900 Hz

SSI2 CLOCK = 1719900 Hz

FIRI CLOCK = 1875000 Hz

CSI CLOCK = 429975 Hz

USB CLOCK = 60000000 Hz

SIM CLOCK = 66500000 Hz

OEMInit: L2 cache is enabled (AUXCR = 0x3001b)

SWITCHING TO HIGH SPEED ARM CLOCK = 532000000 Hz

OEMInit: @@@@@ Version: JS313 @@@@@

KEVIN: Now we use AUO WVGA Display.

OEMInit: @@@@@ LCDInit() @@@@@

OEMInit: @@@@@ OALKitlStart() @@@@@

OEMInit: @@@@@ RNGA_Init(); @@@@@

OEMInit: @@@@@ ConfigureGPIO(); @@@@@

Sp=ffffc7cc

OEMIoControl: Unsupported Code 0x101008c - device 0x0101 func 35

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

///////////////////////////////////////////////////////The normal log of K9F2G08U0CSCB ////////////////////////////////////////////////

Initiating image launch in 0 seconds.

Launching flash image ...

INFO: Using device name: 'MX3117542'

INFO: Reading NK image to NAND (please wait)...

INFO: Copying NK image to RAM address 0xA8100000

INFO: Load is 100% complete.

INFO: Copy of NK completed successfully.

Download successful! Jumping to image at 0x0@(physical 0x80100000)...INFO:OALLogSetZones: g_oalLogMask: 0xb

INFO: PBC Version = 0x0

Windows CE Kernel for ARM (Thumb Enabled) Built on Jun 24 2004 at 18:25:00

ProcessorType=0b36 Revision=4

sp_abt=ffff5000 sp_irq=ffff2800 sp_undef=ffffc800 OEMAddressTable = 88101584

OEMInit: SREV = 0x29

PBC debug switch settings: 0x0

SSI1 clock frequency: pBSPArgs->clockFreq[DDK_CLOCK_SIGNAL_SSI1] = 1719900 Hz

SSI1 clock frequency: mcuPllFreq = 532000000 Hz

SSI1 clock frequency: BSP_CLK_USBPLL_FREQ = 240000000 Hz

SSI1 clock frequency: BSP_CLK_SERPLL_FREQ = 220147200 Hz

SSI1 clock frequency: div = 128

BSP System Configuration:

L2 CACHE ENABLED

MCU PLL = 532000000 Hz

USB PLL = 240000000 Hz

SER PLL = 220147200 Hz

ARM CLOCK = 266000000 Hz

IPU CLOCK = 133000000 Hz

AHB CLOCK = 133000000 Hz

IPG CLOCK = 66500000 Hz

NFC CLOCK = 26600000 Hz

GACC CLOCK = 66500000 Hz

PER CLOCK = 66500000 Hz

SSI1 CLOCK = 1719900 Hz

SSI2 CLOCK = 1719900 Hz

FIRI CLOCK = 1875000 Hz

CSI CLOCK = 429975 Hz

USB CLOCK = 60000000 Hz

SIM CLOCK = 66500000 Hz

OEMInit: L2 cache is enabled (AUXCR = 0x3001b)

SWITCHING TO HIGH SPEED ARM CLOCK = 532000000 Hz

OEMInit: @@@@@ Version: JS313 @@@@@

KEVIN: Now we use AUO WVGA Display.

Sp=ffffc7cc

OEMIoControl: Unsupported Code 0x101008c - device 0x0101 func 35

OEMIoControl: Unsupported Code 0x10100c4 - device 0x0101 func 49

OEMIoControl: Unsupported Code 0x10100c4 - device 0x0101 func 49

GetICHSDataFromReg: mode_lift = 1

CExeUpdateFilesDlg::MainFunc( version 1 ).

watchdog reboot count = 54

Have NOT TestApp.exe in Hard Disk,then judge the data files!

Have NOT DATA File in Hard Disk!

Have TestApp.exe in Nand Disk!

INFO:OALLogSetZones: g_oalLogMask: 0xb

INFO: PBC Version = 0xff

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

Can someone give me some suggestion .

Original Attachment has been moved to: Nandfmd.rar

Original Attachment has been moved to: H27U4G8F2DTR-log.txt.zip

Original Attachment has been moved to: K9F2G08U0CSCB-log.txt.zip

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

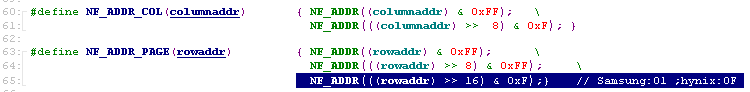

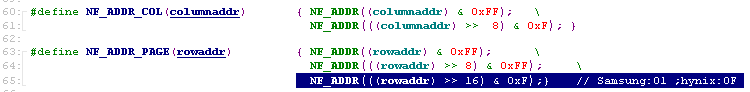

Thank you,I solve this problem now. I find that I ignored to change the description of Address role in the K9F2G08U0A.h ,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi zhang

please try to program nand with atk tool, use attached document

Table 2-3. Example Build Commands for building Flash and Dummy Fuse Libraries,

sect.4.1 Supporting a New Flash Device and atk sources from link:

Programmers (Flash, etc.) (4)

Flash tool for downloading, programing, dumping and erasing images in Flash memory to the i.MX EVK(REV 1.71)

https://www.nxp.com/products/microcontrollers-and-processors/arm-based-processors-and-mcus/i.mx-appl...

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you,I solve this problem now. I find that I ignored to change the description of Address role in the K9F2G08U0A.h ,