# 4Gb NAND FLASH H27U4G8\_6F2D H27S4G8\_6F2D

# **Document Title**

# 4 Gbit (512M x 8 bit) NAND Flash Memory

# **Revision History**

| Revision<br>No. | History                                            | Draft<br>Date  | Remark      |

|-----------------|----------------------------------------------------|----------------|-------------|

| 0.0             | Initial Draft                                      | Jan. 12. 2010  | Preliminary |

| 1.0             | ICC2: Saparate Cache case and normal case          | Mar. 04. 2010  |             |

|                 | tCBSYW value update (5us-Typ.)                     |                |             |

| 1.1             | tCEA -> tCR Typo correction                        | Mar. 31, 2010  |             |

|                 | ICC2 Typcal delete (because of same as max. value) |                |             |

| 1.2             | Adding Bad Block Marking Information               | April 14. 2010 |             |

|                 | Parameter page update                              |                |             |

| 1.3             | Fig. 37 correction                                 | June 29. 2010  |             |

|                 | at least five times -> 3 times in 3.21             |                |             |

| 1.4             | Typo correction D1 -> D in Table. 29               | OCT. 8. 2010   |             |

# FEATURES SUMMARY

#### **DENSITY**

- 4Gbit: 4096blocks

#### **Nand FLASH INTERFACE**

- NAND Interface

- ADDRESS / DATA Multiplexing

#### **SUPPLY VOLTAGE**

- Vcc = 3.0/1.8V Volt core supply voltage for Program, Erase and Read operations.

## **MEMORY CELL ARRAY**

- X8: (2K + 64) bytes x 64 pages x 4096 blocks

- X16: (1k+32) words x 64 pages x 2048 blocks

#### **PAGE SIZE**

- X8: (2048 + 64 spare) bytes

- X16:(1024 + 32spare) Words

#### **Block SIZE**

- X8: (128K + 4K spare) bytes

- X16:(64K + 2K spare) Words

#### **PAGE READ / PROGRAM**

- Random access: 25us (Max)

- Sequentiall access: 25ns / 45ns (3.0V/1.8V, min.)

- Program time(3.0V/1.8V): 200us / 250us (Typ)

- Multi-page program time (2 pages): 200us / 250us (3.0V/1.8V, Typ.)

## **BLOCK ERASE / MULTIPLE BLOCK ERASE**

- Block erase time: 3.5 ms (Typ)

- Multi-block erase time (2 blocks): 3.5ms/ 3.5ms (3.0V/1.8V, Typ.)

#### **SEQURITY**

- OTP area

- Sreial number (unique ID)

- Non-volatile protection option for OTP and Block0(Opt.)

- Hardware program/erase disabled during power transition

#### **ADDTIONAL FEATURE**

- Multiplane Architecture

- : Array is split into two independent planes. Parallel operations on both planes are available, having program and erase time.

- Single and multiplane copy back program with automatic EDC (error detection code)

- Single and multiplane page re-program

- Single and multiplane cache program

- Cache read

- Multiplane block erase

#### Reliability

- 100,000 Program / Erase cycles (with 1bit /528Byte ECC)

B34416/177.179.157.84/2010-10-08 10:08

- 10 Year Data retention

## **ONFI 1.0 COMPLIANT COMMAND SET**

#### **ELECTRONICAL SIGNATURE**

- Munufacture ID: ADh

- Device ID

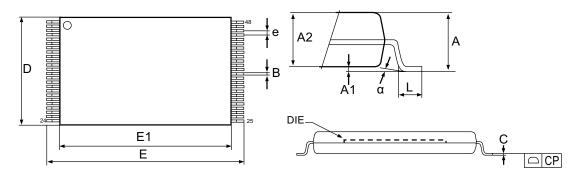

#### **PACKAGE**

- Lead/Halogen Free

- TSOP48 12 x 20 mm

# **CONTENTS**

| 1 Summary Description                                                          | 5  |

|--------------------------------------------------------------------------------|----|

| 1.1 Product List                                                               | 6  |

| 1.2 Pin description                                                            |    |

| 1.3 Functional block diagram                                                   | 9  |

| 1.4 Address role                                                               | 10 |

| 1.5 Command Set                                                                | 11 |

| 2 Bus Operations                                                               | 13 |

| 2.1 Command Input                                                              |    |

| 2.2 Address Input                                                              |    |

| 2.3 Data Input                                                                 |    |

| 2.4 Data Output                                                                |    |

| 2.5 Write Protect                                                              | 13 |

| 2.6 Stand-by                                                                   |    |

| 3 DEVICE OPERATION                                                             |    |

| 3.1 Page Read                                                                  |    |

| 3.2 Data Handiling Restriction During Program Sequences                        |    |

| 3.3 Page Program                                                               |    |

| 3.4 Multiple plane program                                                     | 15 |

| 3.5 Block Erase                                                                | 15 |

| 3.6 Multiple plane Block Erase                                                 | 16 |

| 3.7 Copy-Back Program                                                          |    |

| 3.8 Multiple plane copy back Program                                           |    |

| 3.9 Special read for copy back                                                 |    |

| 3.10 EDC Operation                                                             |    |

| 3.11 Read Status Register                                                      | 19 |

| 3.12 Read Status Enhanced                                                      |    |

| 3.13 Read Status Register field definition                                     |    |

| 3.14 Read EDC Status Register                                                  |    |

| 3.15 Reset                                                                     |    |

| 3.16 Cache Read                                                                |    |

| 3.17 Cache Program                                                             |    |

| 3.18 Multi-plane Cache Program                                                 |    |

| 3.19 Read ID                                                                   |    |

| 3.20 Read ONFI Signature                                                       |    |

| 3.21 Read Parameter Page                                                       |    |

| 3.22 Parameter Page Data Structure Definition                                  |    |

| 4 OTHER FEATURES                                                               |    |

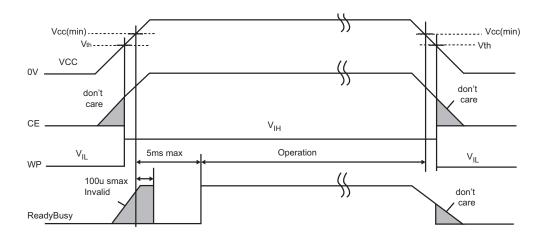

| 4.1 Data Protection and Power on / off sequence                                |    |

| 4.2 Ready/Busy                                                                 |    |

| 4.3 Write protect (#WP) handling                                               |    |

| 5 Device Parameters                                                            |    |

| 6 Timing Diagrams                                                              |    |

| 7 Package Mechanical                                                           |    |

| 7.1 Power consumptions and pin capacitance for allowed stacking configurations |    |

| 8 Application notes and comments                                               |    |

| 8.1 System Interface using CE# don't care                                      |    |

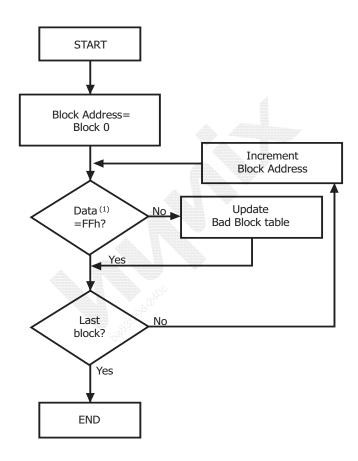

| 8.2 System Bad Block Replacement                                               |    |

| 8.3 Bad Block Management System                                                | 62 |

## 1 Summary Description

H27(U\_S)4G8\_6F2D series is a 512Mx8bit with spare 16Mx8 bit capacity.

The device is offered in 3.0/1.8 Vcc Power Supply, and with x8 and x16 I/O interface

Its NAND cell provides the most cost-effective solution for the solid state mass storage market.

The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data is erased.

The device contains 4096 blocks, composed by 64 pages.

Memory array is split into 2 planes, each of them consisting of 2048 blocks.

Like all other 2KB - page NAND Flash devices, a program operation allows to write the 2112-byte page in typical 200us(3.3V) and an erase operation can be performed in typical 3.5ms on a 128K-byte block.

In addition to this, thanks to multi-plane architecture, it is possible to program 2 pages at a time (one per each plane) or to erase 2 blocks at a time (again, one per each plane). As a consequence, multi-plane architecture allows program time to be reduced by 40% and erase time to be reduction by 50%. In case of multi-plane operation, there is small degradation at 1.8V application in terms of program/erase time.

The multiplane operations are supported both with traditional and ONFI 1.0 protocols.

Data in the page can be read out at 25ns (3V version) and 45nsec (1.8V version) cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command input. This interface allows a reduced pin count and easy migration towards different densities, without any rearrangement of footprint.

Commands, Data and Addresses are synchronously introduced using CE#, WE#, ALE and CLE input pin.

The on-chip Program/Erase Controller automates all read, program and erase functions including pulse repetition, where required, and internal verification and margining of data.

A WP# pin is available to provide hardware protection against program and erase operations.

The output pin RB# (open drain buffer) signals the status of the device during each operation. In a system with multiple memories the RB# pins can be connected all together to provide a global status signal.

Each block can be programmed and erased up to 100,000 cycles with ECC (error correction code) on. To extend the lifetime of Nand Flash devices, the implementation of an ECC is mandatory.

The chip supports CE# don't care function. This function allows the direct download of the code from the NAND Flash memory device by a microcontroller, since the CE# transitions do not stop the read operation.

In addition, device supports ONFI 1.0 specification.

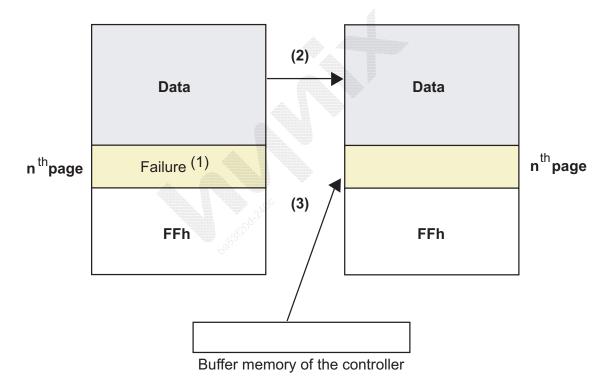

The copy back function allows the optimization of defective blocks management: when a page program operation fails the data can be directly programmed in another page inside the same array section without the time consuming serial data insertion phase. Copy back operation automatically executes embedded error detection operation: 1 bit error out of every 528-byte (x8) or 1 bit error out of every 264-word (x16) can be detected. With this feature it is no longer necessary to use an external to detect copy back operation errors.

Multiplane copy back is also supported, both with traditional and ONFI 1.0 protocols. Data read out after copy back read (both for single and multiplane cases) is allowed.

In addition, Cache program and multi cache program operations improve the programing throughput by programing data using the cache register.

The devices provide two innovative features: page re-program and multiplane page re-program. The page re-program allows to re-program one page. Normally, this operation is performed after a previously failed page program operation. Similarly, the multiplane page re-program allows to re-program two pages in parallel, one per each plane. The first page must be in the first plane while the second page must be in the second plane; the multiplane page re-program operation is performed after a previously failed multiplane page program operation. The page re-program and multiplane

page re-program guarantee imporve performance, since data insertion can be omitted during re-program operations, and save ram buffer at the host in the case of program failure.

The devices, available in the TSOP48 (12X20mm) package, support the ONFI1.0 specification and come with four sequrity features:

- OTP (one time programmable) area, which is a restricted access area where sensitive data/code can be stored permantely.

- Serial number (unique identifier), which allows the devices to be nuniquely indentified.

- Read ID2 extention

- Non-volatile protection to lock sensible data permanently.

These security features are subject to an NDA (non-disclosure agreement) and are, therefore, no described in the datasheet. For more details about them, contact your nearest Hynix sales office.

## 1.1.Product List

| PART NUMBER | ORGANIZATION | Operating RANGE | PACKAGE |

|-------------|--------------|-----------------|---------|

| H27U4G8F2D  | x8           | 2.7 to 3.6V     | -       |

| H27U4G6F2D  | x16          | 2.7 to 3.6V     | -       |

| H27S4G8F2D  | x8           | 1.7 to 1.95V    | -       |

| H27S4G6F2D  | x16          | 1.7 to 1.95V    | -       |

Table 1: list of supported versions / packages

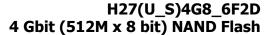

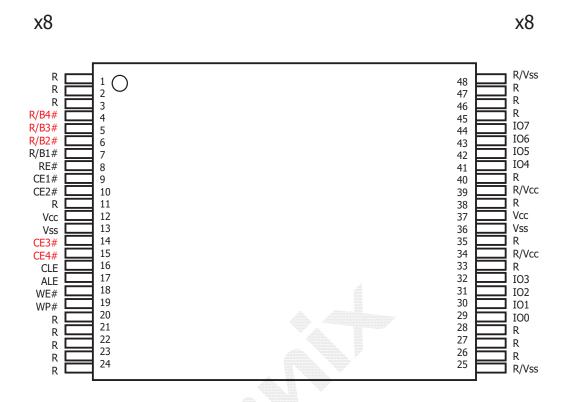

Figure 1: Logic Diagram

| DQ7 - DQ0       | Data Input / Outputs (x8/x16) |

|-----------------|-------------------------------|

|                 | , , , , , ,                   |

| DQ15 - DQ8      | Data Input / Outputs (x16)    |

| CLE             | Command latch enable          |

| ALE             | Address latch enable          |

| CE#             | Chip Enable                   |

| RE#             | Read Enable                   |

| WE#             | Write Enable                  |

| WP#             | Write Protect                 |

| RB#             | Ready/ Busy                   |

| V <sub>CC</sub> | Power supply                  |

| V <sub>SS</sub> | Ground                        |

| NC              | No Connected internally       |

**Table 2: Signal Names**

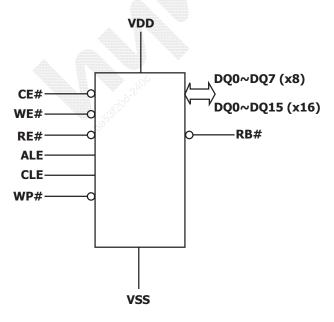

Figure 2. 48TSOP1 Contact, x8 and x16 Devic

## 1.2 PIN DESCRIPTION

| Pin Name        | Description                                                                                                                                                                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ0 - DQ15      | <b>DATA INPUTS/OUTPUTS</b> The DQ pins allow to input command, address and data and to output data during read / program operations. The inputs are latched on the rising edge of Write Enable (WE#). The I/O buffer float to High-Z when the device is deselected or the outputs are disabled. |

| CLE             | COMMAND LATCH ENABLE  This input activates the latching of the DQ inputs inside the Command Register on the Rising edge of Write Enable (WE#).                                                                                                                                                  |

| ALE             | ADDRESS LATCH ENABLE  This input activates the latching of the DQ inputs inside the Command Register on the Rising edge of Write Enable (WE#).                                                                                                                                                  |

| CE#             | CHIP ENABLE This input controls the selection of the device. When the device is busy CE# low does not deselect the memory.                                                                                                                                                                      |

| WE#             | WRITE ENABLE This input acts as clock to latch Command, Address and Data. The DQ inputs are latched on the rise edge of WE#.                                                                                                                                                                    |

| RE#             | <b>READ ENABLE</b> The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE# which also increments the internal column address counter by one.                                                           |

| WP#             | WRITE PROTECT The WP# pin, when Low, provides an Hardware protection against undesired modify (program / erase) operations.                                                                                                                                                                     |

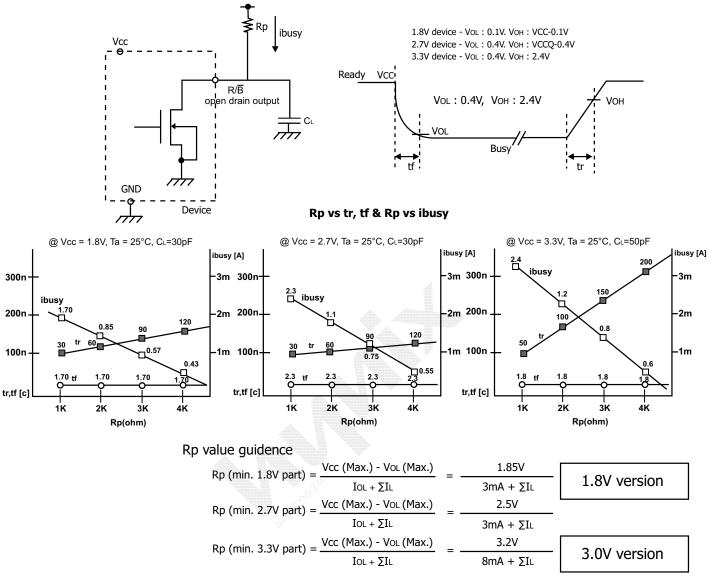

| RB#             | <b>READY BUSY</b> The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                                                                                                                              |

| V <sub>CC</sub> | SUPPLY VOLTAGE FOR IO BUFFER  The $V_{CC}$ supplies the power for all the operations (Read, Write, Erase). An internal lock circuit prevent the insertion of Commands when $V_{CC}$ is less than $V_{LKO}$                                                                                      |

| $V_{SS}$        | GROUND                                                                                                                                                                                                                                                                                          |

| NC / DNU        | NO CONNECTED / DON'T USE                                                                                                                                                                                                                                                                        |

**Table 3: Pin Description**

#### NOTE:

- 1. A 0.1 uF capacitor should be connected between the  $V_{CC}$  Supply Voltage pin and the VSS Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

- 2. an internal voltage detector disables all functions whenever  $V_{CC}$  is below 1.8V (3V version) or 1.1V (1.8V) version to protect the device from any involuntary program/erase during power transitions.

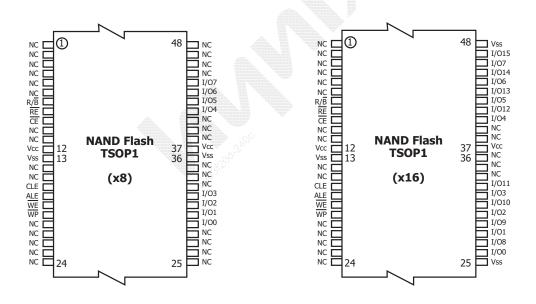

# 1.3 Functional block diagram

Figure 3: block description

## 1.4 Address role

|                           | DQ0 | DQ1 | DQ2 | DQ3 | DQ4 | DQ5 | DQ6 | DQ7 |

|---------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1 <sup>st</sup> Cycle     | A0  | A1  | A2  | A3  | A4  | A5  | A6  | A7  |

| 2 <sup>nd</sup> Cycle     | A8  | A9  | A10 | A11 | 0   | 0   | 0   | 0   |

| 3 <sup>rd</sup> Cycle     | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 |

| 4 <sup>th</sup> Cycle     | A20 | A21 | A22 | A23 | A24 | A25 | A26 | A27 |

| 5 <sup>th</sup> Cycle (*) | A28 | A29 | A30 | A31 | 0   | 0   | 0   | 0   |

Table 4: Address Cycle Map (x8)

(\*): A30 for 8Gbit DDP(1CE). A30:A31 for 16Gbit QDP(1CE).

As far as the address bits are concerned, the following rules apply:

A0 - A11 : column address in the page A12 - A17 : page address in the block

A18: plane address (for multi-plane operations) / block address (for normal operations)

A19 - A31 : block address

|                           | DQ0 | DQ1 | DQ2 | DQ3 | DQ4 | DQ5 | DQ6 | DQ7 |

|---------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1 <sup>st</sup> Cycle     | A0  | A1  | A2  | A3  | A4  | A5  | A6  | A7  |

| 2 <sup>nd</sup> Cycle     | A8  | A9  | A10 | 0   | 0   | 0   | 0   | 0   |

| 3 <sup>rd</sup> Cycle     | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 |

| 4 <sup>th</sup> Cycle     | A19 | A20 | A21 | A22 | A23 | A24 | A25 | A26 |

| 5 <sup>th</sup> Cycle (*) | A27 | A28 | A29 | A30 | 0   | 0   | 0   | 0   |

Table 5: Address Cycle Map (x16)

(\*): A29 for 8Gbit DDP(1CE). A29:A30 for 16Gbit QDP(1CE)

As far as the address bits are concerned, the following rules apply:

A0 - A10 : column address in the page A11 - A16 : page address in the block

A17: plane address (for multi-plane operations) / block address (for normal operations)

A18 - A30 : block address

## 1.5 Command Set

| Command <sup>(1)</sup>                                      | 1 <sup>st</sup> CYCLE | 2 <sup>nd</sup> CYCLE | 3 <sup>rd</sup> CYCLE | 4 <sup>th</sup> CYCLE | Acceptable command during busy |

|-------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------------------------------|

| READ                                                        | 00h                   | 30h                   |                       |                       |                                |

| READ FOR COPY-BACK                                          | 00h                   | 35h                   |                       |                       |                                |

| SPECIAL READ FOR COPY BACK                                  | 00h                   | 36h                   |                       |                       |                                |

| READ ID                                                     | 90h                   |                       |                       |                       |                                |

| READ ID2                                                    | 30h-65h-00h           | 30h                   |                       |                       |                                |

| RESET                                                       | FFh                   |                       |                       |                       | Yes <sup>(2)</sup>             |

| PAGE PGM (start) / CACHE PGM (end)                          | 80h                   | 10h                   |                       |                       |                                |

| CACHE PGM (Start) / (continue)                              | 80h                   | 15h                   |                       |                       |                                |

| PAGE REPROGRAM / N <sup>th</sup> PAGE CACHE REPROGRAM (end) | 8Bh                   | 10h                   |                       |                       |                                |

| N <sup>th</sup> PAGE CACHE REPROGRAM (continue)             | 8Bh                   | 15h                   |                       |                       |                                |

| N-1 <sup>th</sup> PAGE CACHE REPROGRAM (continue)           | 8Ah                   | 15h                   |                       |                       |                                |

| COPY BACK PGM (start)                                       | 85h                   | 10h                   |                       |                       |                                |

| (Traditional) MULTI PLANE PROGRAM <sup>(3)</sup>            | 80h                   | 11h                   | 81h                   | 10h                   |                                |

| ONFI MULTIPLANE PROGRAM                                     | 80h                   | <b>11</b> h           | 80h                   | 10h                   |                                |

| MULTIPLANE PAGE RE-PROGRAM                                  | 8Bh                   | 11h                   | 8Bh                   | 10h                   |                                |

| (Traditional) MULTIPLANE CACHE PGM (start/cont)             | 80h                   | 11h                   | 81h                   | 15h                   |                                |

| ONFI MULTIPLANE CACHE PGM (start/cont)                      | 80h                   | 11h                   | 80h                   | 15h                   |                                |

| (Traditional) MULTIPLANE CACHE PGM (end) <sup>(3)</sup>     | 80h                   | 11h                   | 81h                   | 10h                   |                                |

| ONFI MULTIPLANE CACHE PGM (end)                             | 80h                   | 11h                   | 80h                   | 10h                   |                                |

| N <sup>th</sup> PAGES MULTIPLANE CACHE RE-PROGRAM (cont)    | 8Bh                   | 11h                   | 8Bh                   | 15h                   |                                |

| N <sup>th</sup> PAGES MULTIPLANE CACHE RE-PROGRAM (end)     | 8Bh                   | 11h                   | 8Bh                   | 10h                   |                                |

| N-1 <sup>th</sup> PAGES MULTIPLANE CACHE RE-PROGRAM (cont)  | है 8Ah                | 11h                   | 8Ah                   | 15h                   |                                |

| (Traditional) MULTI PLANE COPY BACK PROGRAM <sup>(3)</sup>  | <sup>5</sup> 85h      | 11h                   | 81h                   | 10h                   |                                |

| ONFI MULTIPLANE COPYBACK PGM                                | 85h                   | 11h                   | 85h                   | 10h                   |                                |

| BLOCK ERASE                                                 | 60h                   | D0h                   |                       |                       |                                |

| (Traditional) MULTI PLANE BLOCK ERASE <sup>(3)</sup>        | 60h                   | 60h                   | D0h                   |                       |                                |

| ONFI MULTIPLANE BLOCK ERASE                                 | 60h                   | D1h                   | 60h                   | D0h                   |                                |

| READ STATUS REGISTER                                        | 70h                   |                       |                       |                       | Yes                            |

| READ STATUS ENHANCED                                        | 78h                   |                       |                       |                       | Yes                            |

| RANDOM DATA INPUT                                           | 85h                   |                       |                       |                       |                                |

| RANDOM DATA OUTPUT                                          | 05h                   | E0h                   |                       |                       |                                |

| CACHE READ(SEQUENTIAL)                                      | 31h                   |                       |                       |                       |                                |

| CACHE READ ENHANCED (RANDOM)                                | 00h                   | 31h                   |                       |                       |                                |

| CACHE READ END                                              | 3Fh                   |                       |                       |                       |                                |

| READ PARAMETER PAGE                                         | Ech                   |                       |                       |                       |                                |

| EDC STATUS READ                                             | 7Bh                   |                       |                       |                       | V                              |

| EXTENDED READ STATUS                                        | F2h/F3h/F4h/F5h       |                       |                       |                       | Yes                            |

**Table 6: Public Command Set**

## NOTE:

- 1. Commands listed in BOLD are referring to ONFI 1.0 Specification.

- 2. Only during cache ready busy.

- 3. Command maintained for backward compatibility

| CLE | ALE | CE#              | WE#    | RE#     | WP#                   |                    | MODE                           |  |

|-----|-----|------------------|--------|---------|-----------------------|--------------------|--------------------------------|--|

| Н   | L   | L                | Rising | Н       | Х                     | Read               | Command Input                  |  |

| L   | Н   | L                | Rising | Н       | Х                     | Mode               | Address Input                  |  |

| Н   | L   | L                | Rising | Н       | Н                     | Write              | Command Input                  |  |

| L   | Н   | L                | Rising | Н       | Н                     | Mode               | Address Input                  |  |

| L   | L   | L                | Rising | Н       | Н                     | Data Input         |                                |  |

| L   | L   | L <sup>(1)</sup> | Н      | Falling | Х                     | Data Out           | put (on going)                 |  |

| Х   | Х   | L <sup>(1)</sup> | Н      | Н       | Х                     | Data Out           | put (suspended) <sup>(2)</sup> |  |

| L   | L   | L                | Н      | Н       | Х                     | Busy time          | e in Read                      |  |

| Х   | Х   | Х                | Х      | Х       | Н                     | Busy time          | e in Program                   |  |

| Х   | Х   | Х                | Х      | Х       | H                     | Busy time in Erase |                                |  |

| Х   | Х   | Х                | Х      | X       | L                     | Write Pro          | Write Protect                  |  |

| Χ   | Х   | Н                | Х      | Χ       | 0 V / V <sub>CC</sub> | Stand By           |                                |  |

**Table7: Mode Selection**

## **NOTES:**

1. As 4Gbit SLC F41 is CE# don't care device, CE# high during latency time does not stop the read operation.

## 2. BUS OPERATION

There are six standard bus operationTable 28s that control the device. These are Command Input, Address Input, Data Input, Data Output, Write PrTable 28otect, and Standby. (see **Figure 1** and **Table 6**)

Typically glitches less than 5 ns on Chip Enable, Write Enable and Read Enable are ignored by the memory and do not affect bus operations.

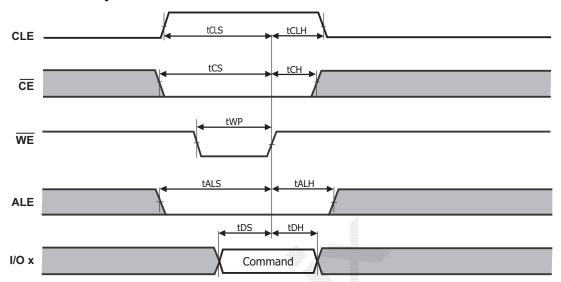

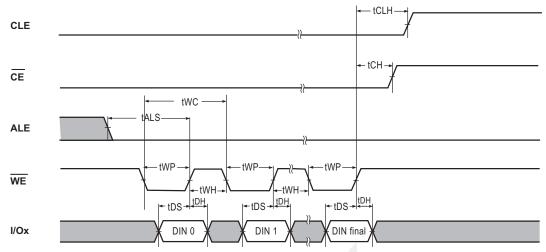

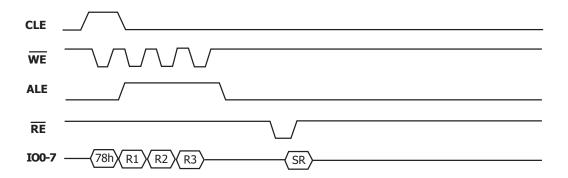

#### 2.1. Command Input

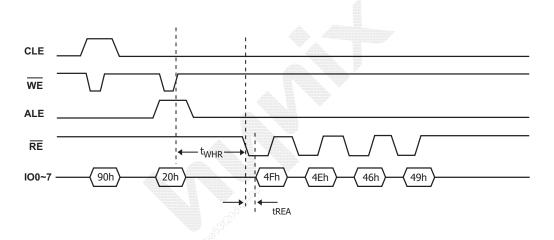

Command Input bus operation is used to give a command to the memory device. Command are accepted with Chip Enable low, Command Latch Enable High, Address Latch Enable low and Read Enable High and latched on the rising edge of Write Enable. Moreover for commands that starts a modify operation (write/erase) the Write Protect pin must be high. See **Figure 5** and **Table 28** for details of the timings requirements. Command codes are always applied on IO7:0 regardless of the bus configuration. (X8 or X16)

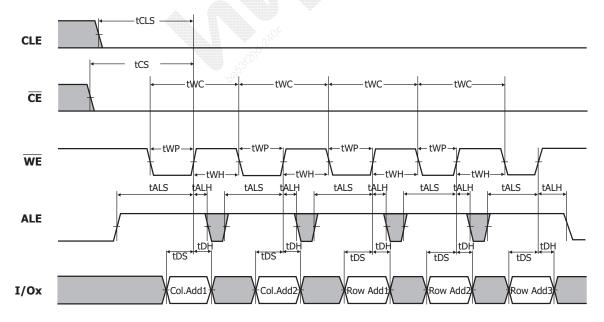

#### 2.2. Address Input

Address Input bus operation allows the insertion of the memory address. 5 clock cycles are needed to input the addresses. Addresses are accepted with Chip Enable low, Address Latch Enable High, Command Latch Enable low and Read Enable High and latched on the rising edge of Write Enable. Moreover for commands that starts a modify operation (write/erase) the Write Protect pin must be high. See **Figure 5** and **Table 28** for details of the timings requirements. Addresses are always applied on IO7:0 regardless of the bus configuration. (X8 or X16). Refer to **Table 4** and **Table 5** for more detailed information.

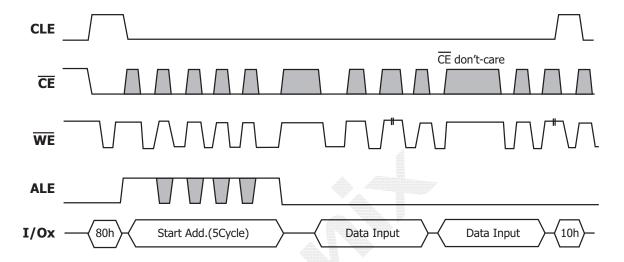

## 2.3. Data Input

Data Input bus operation allows to feed to the device the data to be programmed. The data insertion is serial and timed by the Write Enable cycles. Data are accepted only with Chip Enable low, Address Latch Enable low, Command Latch Enable low, Read Enable High, and Write Protect High and latched on the rising edge of Write Enable. See **Figure 7** and **Table 28** for details of the timings requirements.

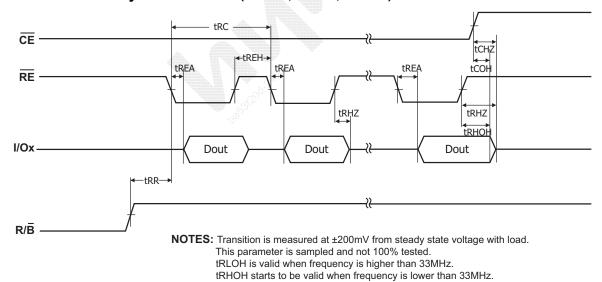

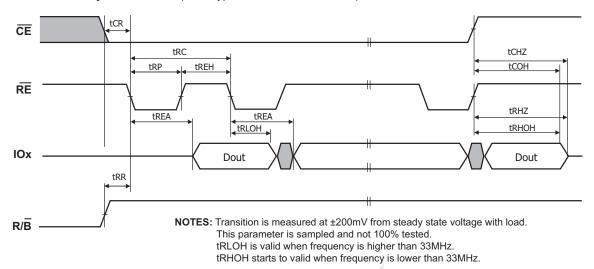

## 2.4. Data Output

Data Output bus operation allows to read data from the memory array and to check the status register content, the EDC register content and the ID data. Data can be serially shifted out by toggling the Read Enable pin with Chip Enable low, Write Enable High, Address Latch Enable low, and Command Latch Enable low. See **Figure 8** to **Figure 11** and **Table 28** for details of the timings requirements.

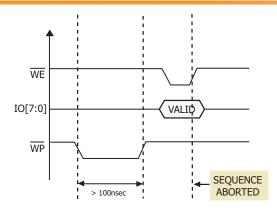

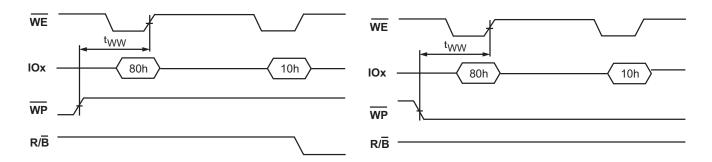

## 2.5. Write Protect

Hardware Write Protection is activated when the Write Protect pin is low. In this condition modify operation do not start and the content of the memory is not altered. Write Protect pin is not latched by Write Enable to ensure the protection even during the power up.

## 2.6. Standby

In Standby the device is deselected, outputs are disabled and Power Consumption is reduced.

## 3. DEVICE OPERATION

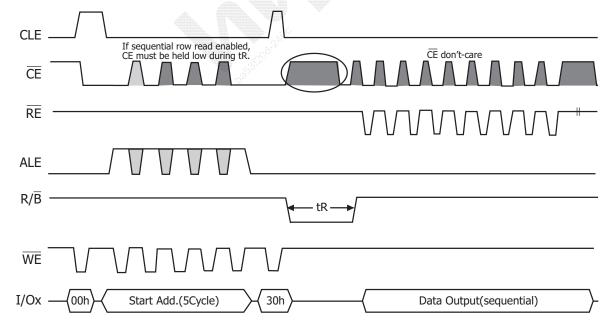

#### 3.1. Page Read

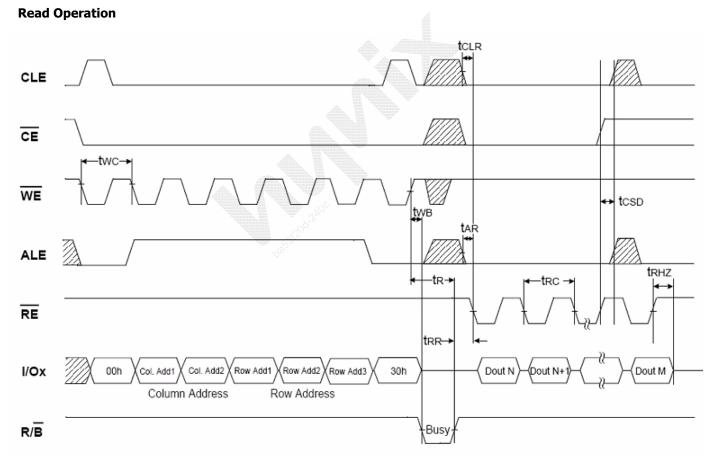

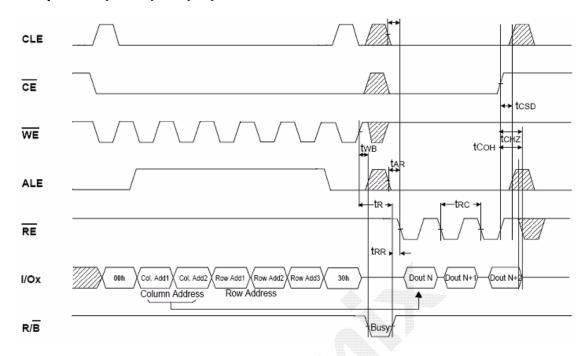

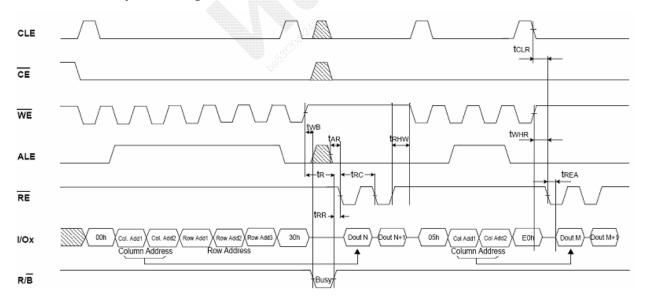

This operation is initiated by writing 00h and 30h to the command register along with five address cycles. Two types of operations are available: random read, serial page read. The random read mode is enabled when the page address is changed. The 2112 bytes (x8) or 1056 (x16) of data within the selected page are transferred to the data registers in less than 25us(tR). The system controller may detect the completion of this data transfer (tR) by analyzing the output of R/B pin. Once the data in a page is loaded into the data registers, they may be read out in 25ns (3V version) and 45nsec (1.8V version) cycle time by sequentially pulsing RE#. The repetitive high to low transitions of the RE# clock make the device output the data starting from the selected column address up to the last column address.

The device may output random data in a page instead of the sequential data by writing random data output command. The column address of next data, which is going to be out, may be changed to the address which follows random data output command.

Random data output can be operated multiple times regardless of how many times it is done in a page.

After power up device is in read mode, so 00h command cycle is not necessary to start a read operation. Any operation other than read or random data output causes device to exit read mode.

Check Figure 12, Figure 13, Figure 14 as references.

## 3.2 Data handling restirctions during program sequences

Applications which use the error detection code in copy back must respect some restrictions related to data handling during program sequence.

The error dection code check is used during copy back program and multiplane copy back program operations to detect single bit errors pccurred in the source page (for details about EDC)

Note: The restrictions described below are not valid if the application uses the copy back program or multiplane copy back program without EDC check.

When data handling is performed, the page program, multiplane page program, page re-program, multiplane page reprogram, cache ptrgram and multiplane cache program operations, must respect the following restrictions:

- 1. Program operations must be performed on the whole page, or on the whole EDC unit at a time.

- 2. For each program operation, random data input can be executed only once for each EDC unit.

Copy back program or multiplane copy back program opeations must respect the following restrictions:

- 1. If rando, data input is applied in a given EDC unit, the data of the whole EDC unit must be inserted. In ohter words, the EDC check is possible only if the whole EDC unit is modified during a copy back program sequence.

- 2. For each program operation, rando, data input can be executed only once for each EDC unit.

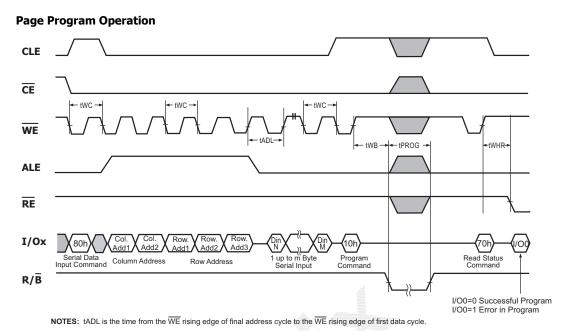

## 3.3 Page Program

A page program cycle consists of a serial data loading period in which up to 2112 bytes of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell.

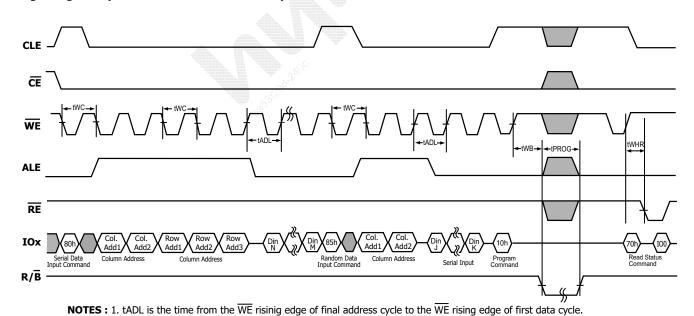

The serial data loading period begins by inputting the Serial Data Input command (80h), followed by the five cycle address inputs and then serial data. The words other than those to be programmed do not need to be loaded. The device supports random data input within a page. The column address of next data, which will be entered, may be changed to the address which follows random data input command (85h). Random data input may be operated multiple times regardless of how many times it is done in a page.

The Page Program confirm command (10h) initiates the programming process. The internal write state controller automat-

ically executes the algorithms and controls timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register commands (70h or 78h) may be issued to read the status register. The system controller can detect the completion of a program cycle by monitoring the RB# output, or the Status bit (I/O 6) of the Status Register. Only the Read Status commands (70h or 78h) or Reset command are valid during programming is in progress. When the Page Program is complete, the Write Status Bit (I/O 0) may be checked. The internal write verify detects only errors for "1"s that are not successfully programmed to "0"s. The command register remains in Read Status command mode until another valid command is written to the command register. Figure 14 and Figure 15 detail the sequence.

The device is programmed basically by page, but it also allows multiple partial page programming of a word or consecutive bytes up to 2112 (x8) or 1056 (x16) in a single page program cycle.

The number of consecutive partial page programming operations (NOP) within the same page must not exceed the number indicated in **Table 27**. In addition, pages must be sequentially programmed within a block.

Users which use "EDC check" in copy back must comply with some limitations related to data handling during one page program sequence. Please refer to Section 3.10 for details.

## 3.4. Multiple plane program

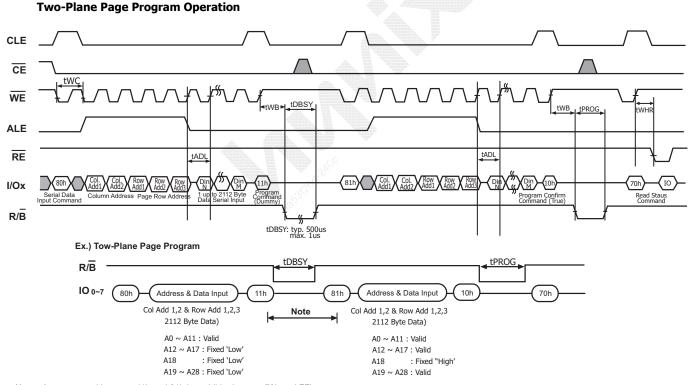

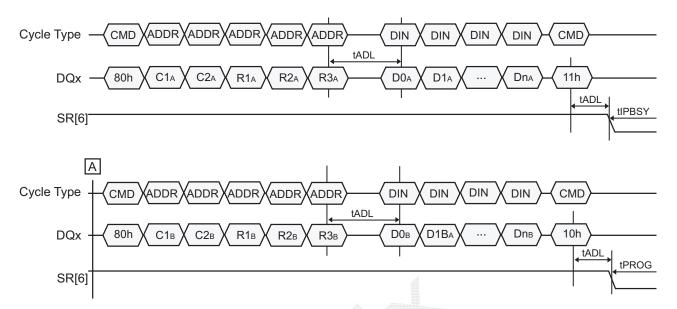

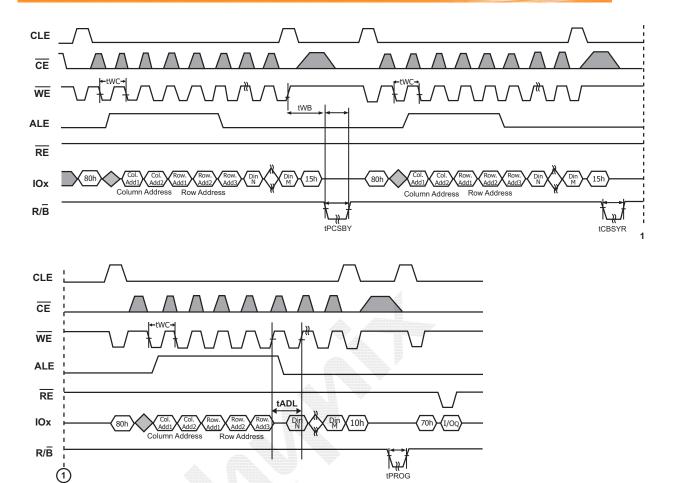

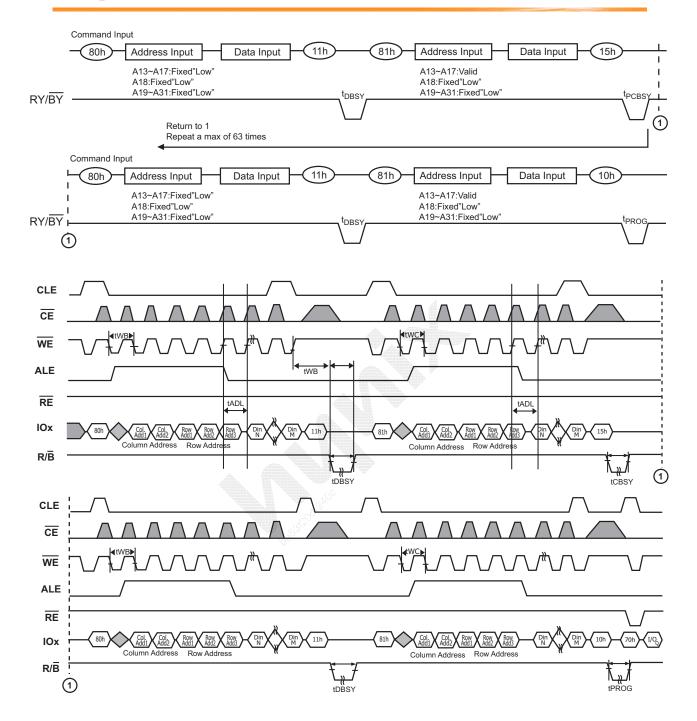

Device supports multiple plane program: it is possible to program 2 pages in parallel, one per each plane. A multiple plane program cycle consists of a double serial data loading period in which up to 4224bytes of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell. The serial data loading period begins with inputting the Serial Data Input command (80h), followed by the five cycle address inputs and serial data for the  $1^{\rm st}$  page. Address for this page must be in the  $1^{\rm st}$  plane (A<18>=0). The device supports random data input exactly same as in the case of page program operation. The Dummy Page Program Confirm command (11h) stops  $1^{\rm st}$  page data input and devices becomes busy for a short time ( $t_{\rm DBSY}$ ). Once it has become ready again, either the traditional "81h" or the ONFI 1.0 "80h" command must be issued, followed by  $2^{\rm nd}$  page address (5 cycles) and its serial data input. Address for this page must be in the  $2^{\rm nd}$  plane (A<18>=1). Program Confirm command (10h) makes parallel programming of both pages to start. **Figure 20** and **Figure 21** describe the sequences.

User can check operation status by monitoring RB# pin or reading status register commands (70h or 78h), as if it were a normal page program: read status register command is also available during Dummy Busy time ( $t_{DBSY}$ ). In case of fail in any of 1<sup>st</sup> and 2<sup>nd</sup> page program, fail bit of status register will be set however, in order to know which page failed, ONFI 1.0 "read status enhanced" command must be issued Refer to **section 3.11** for further info.

The number of consecutive **partial page programming operations** (NOP) within the same page must not exceed the number indicated in **Table 27.** In addition, it is recommended to program pages sequentially within a block.

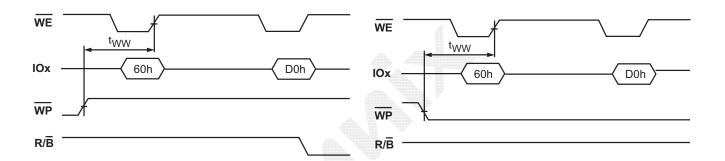

#### 3.5. Block Erase

The Block Erase operation is done on a block basis. Block address loading is accomplished in 3 cycles initiated by an Erase Setup command (60h). Only addresses A18 to A29 are valid while A12 to A17 are ignored. The Erase Confirm command (D0h) following the block address loading initiates the internal erasing process This two-step sequence of setup followed by execution command ensures that memory contents are not accidentally erased due to external noise conditions.

At the rising edge of WE# after the erase confirm command input, the internal write controller handles erase and erase-verify.

Once the erase process starts, the Read Status Register commands (70h or 78h) may be issued to read the status register. The system controller can detect the completion of an erase by monitoring the RB# output, or the Status bit (I/O 6) of the Status Register. Only the Read Status commands (70h or 78h) and Reset command are valid while erasing is in progress. When the erase operation is completed, the Write Status Bit (I/O 0) may be checked.

Figure 19 details the sequence.

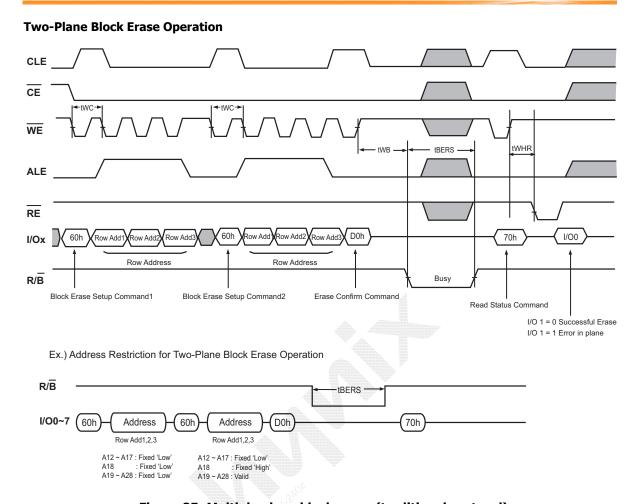

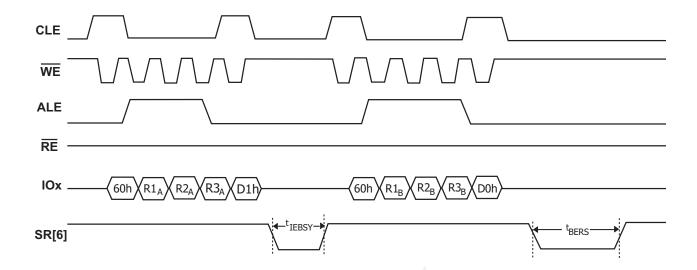

## 3.6. Multiple plane Block Erase

Multiple plane erase, allows parallel erase of two blocks in parallel, one per each memory plane.

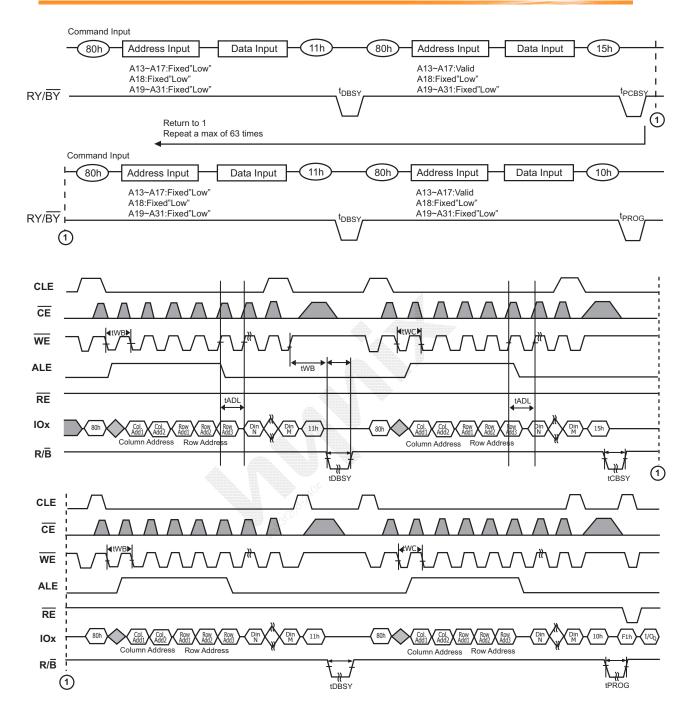

Two different command sequences are allowed in these case, traditional and ONFI 1.0.

In traditional case, Block erase setup command (60h) must be repeated two times, followed by 1<sup>st</sup> and 2<sup>nd</sup> block address respectively (3 cycles each). As for block erase, D0h command makes embedded operation to start.

In this case, multiplane erase does not need any Dummy Busy Time between  $1^{st}$  and  $2^{nd}$  block insertion. See **Figure 25** for details.

checked like in the multiple plane program through Read Status Register, or ONFI 1.0 Read Status Enhanced.

As an alternative, the ONFI 1.0 multiplane command protocol can be used, with 60h erase setup followed by  $1^{st}$  block address and D1h first confirm, 60h erase setup followed by  $2^{nd}$  block address and D0h (multiplane confirm). Between the two block-related sequences, a short busy time  $t_{IEBSY}$  will occur. See **Table 27** and **Figure 26** for details. Address limitation required for multiple plane program applies also to multiple plane erase. Also operation progress can be

As for multiplane page program, the address of the first second page must be within the first plane (A18=0 for x8 devices, A17=0 for x16 devices) and second plane (A18 = 1 for devices, A17=1 for x16 devices), respectively.

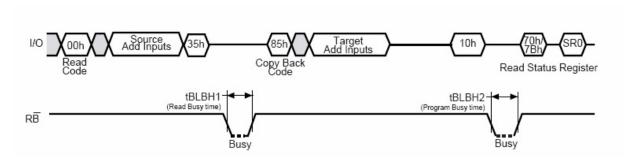

## 3.7. Copy-Back Program.

The copy-back program is configured to quickly and efficiently rewrite data stored in one page without utilizing an external memory. Since the time-consuming cycles of serial access and re-loading cycles are removed, the system performance is greatly improved. The benefit is especially obvious when a portion of a block needs to be updated and the rest of the block also need to be copied to the newly assigned free block. The operation for performing a copy-back program is a sequential execution of page-read (without mandatory serial access) and copy back -program with the address of destination page. A read operation with "35h" command and the address of the source page moves the whole 2112byte data into the internal data buffer. As soon as the device returns to Ready state, optional data read-out is allowed by toggling RE# (see **Figure 17**), or Copy Back command (85h) with the address cycles of destination page may be written. The Program Confirm command (10h) is required to actually begin the programming operation.

Source and Destination page in the copy back program sequence must belong to the same device plane (x8 : same A18, x16 : same A17)

Data input cycle for modifying a portion or multiple distant portions of the source page is allowed as shown in **Figure 18.** This device includes automatic Error Detection Code check during copy back operation, to detect single bit errors in EDC units occurred in the source page.

More details on EDC operation, and limitation related to data input handling during one copy back program sequence are available in **section 3.10**

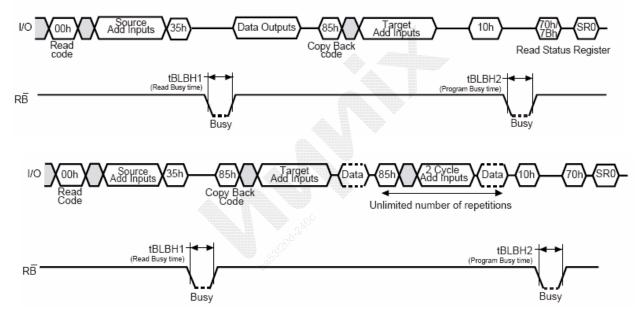

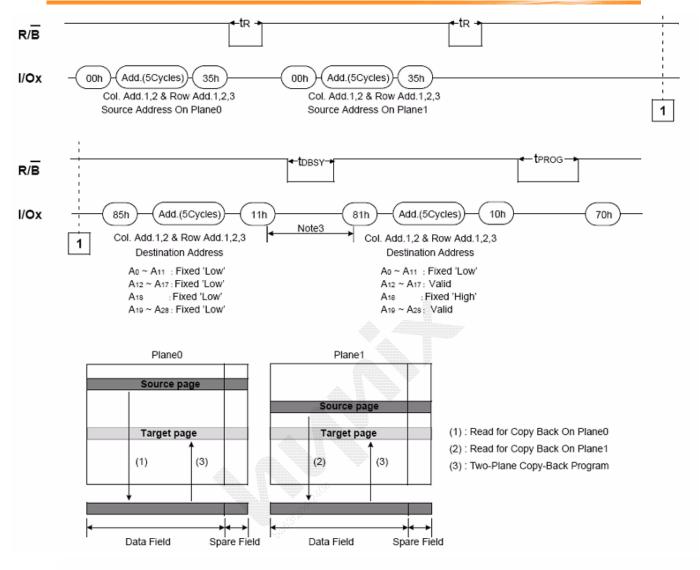

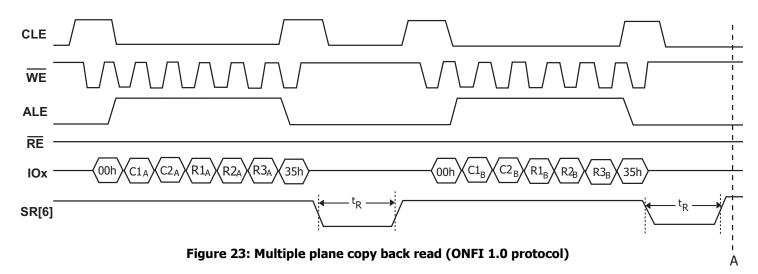

## 3.8. Multiple plane copy back Program

As for page program, device supports Multi-plane copy back program with exactly same sequence and limitations. Multi-plane copy back program must be preceded by 2 single page read for copy back command sequences (1<sup>st</sup> page must be read from the 1<sup>st</sup> plane and 2<sup>nd</sup> page from the 2<sup>nd</sup> plane).

Multi-plane copy back cannot cross plane boundaries: the contents of the source page of one device plane can be copied only to a destination page of the same plane.

EDC check is available also for multi-plane copy back program.

Users which use "EDC check" in copy back must comply with some limitations related to data handling during one multiplane copy back program sequence. Please refer to **Section 3.10** for details.

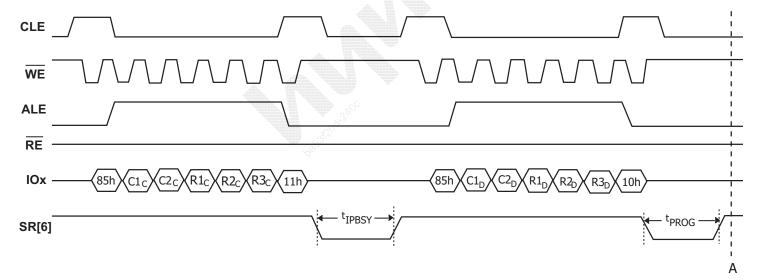

Also in this case, two different sequences are allowed: the traditional one (85h, first plane address 11h, 81h, second plane address, 10h) represented in **Figure 22**, and ONFI 1.0 sequence (85h, first plane address 11h, 85h, second plane address, 10h) represented in **Figure 23** and **Figure 24**.

## 3.9. Special read for copy back

The device feature the "special read for copy back".

If copy back read (described in **sections 3.7** and **3.8**) is triggered with confirm command "36h" instead "35h", copy back read from target page(s) will be executed with an increased internal (Vpass) voltage.

This special feature is used in order to try to recover incorrigible ECC read errors due to over-program or read disturb: it shall be used ONLY if ECC read errors have occurred in the source page using "standard read" or "standard read for copy back" sequences..

Excluding the copy-back read confirm command, all other features described in **sections 3.7** and **3.8** for standard copy back remain valid (including the figures referred to in those sections).

## 3.10. EDC operation

Error Detection Code check is a feature which be used during copy back program operation (both single and multiplane) to detect single bit errors occurred in the source page (s).

- In the x8 version EDC check allows detection of up to 1 single bit error every 528 bytes, where each 528 byte group is composed by 512 byte of main array and 16 bytes of spare area (see **Table 8** and **Table 9**). The described 528 byte area is called "EDC unit".

- In the x16 version EDC allows detection of up to 1 single bit error every 264 words, where each 264 word group is composed by 256 words of main array and 8 words of spare area (see **Table 10** and **Table 11**). The described 264 word area is called "EDC unit".

EDC result can be checked through specific Read EDC register command, available only during copy back program and only for the device version supporting ECC=1. EDC register can be queried during the copy back program busy time.  $(t_{PROG})$

For "EDC check" feature to operate correctly specific conditions on data input handling apply for page program and copy back program (single, cached, multi-plane):

For the case of page program

- 1) In section 3.2 it was explained that a number of consecutive partial program operations (NOP) is allowed within the same page. In case this feature is used, the number of partial program operations occurring in the same EDC unit must not exceed "one" (1). In other words, page program operations must be performed on the whole page, or on whole EDC unit at a time.

- 2) "random data input" in a given EDC unit can be executed several times during one page program sequence, but data insertion in each column address of each EDC unit must not exceed "one" (1).

For the case of copy back program

- 1) If random data input is applied in a given EDC unit, the data of the whole EDC unit must be inserted. In other words, the EDC check is possible only if the whole EDC unit is modified during one copy back program sequence

- 2) "random data input" in a given EDC unit can be executed several times during one copy back sequence, but data insertion in each column address of the EDC unit must not exceed "one" (1)

For the user which use Copy Back without EDC check, all the limitations described above do not apply.

|                          | Spare Field (64 Byte)    |                                     |                                     |                          |                          |                          |                          |

|--------------------------|--------------------------|-------------------------------------|-------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| "A"area                  | "B"area                  | "E"area                             | "F"area                             | "G"area                  | "H"area                  |                          |                          |

| (1 <sup>st</sup> sector) | (2 <sup>nd</sup> sector) | "C"area<br>(3 <sup>rd</sup> sector) | "D"area<br>(4 <sup>th</sup> sector) | (1 <sup>st</sup> sector) | (2 <sup>nd</sup> sector) | (3 <sup>rd</sup> sector) | (4 <sup>th</sup> sector) |

| 512 Byte                 | 512 Byte                 | 512 Byte                            | 512 Byte                            | 16 Byte                  | 16 Byte                  | 16 Byte                  | 16 Byte                  |

Table 8: page organization in EDC units (x8)

| Sector                          | Main Field (Co | olumn 0~2047)  | Spare Field (Column 2048~2111) |                |  |  |

|---------------------------------|----------------|----------------|--------------------------------|----------------|--|--|

| Sector                          | Area Name      | Column Address | Area Name                      | Column Address |  |  |

| 1 <sup>st</sup> 528-Byte Sector | "A"            | 0~511          | "E"                            | 2048~2063      |  |  |

| 2 <sup>nd</sup> 528-Byte Sector | "B"            | 512~1023       | "F"                            | 2064~2079      |  |  |

| 3 <sup>rd</sup> 528-Byte Sector | "C"            | 1024~1535      | "G"                            | 2080~2095      |  |  |

| 4 <sup>th</sup> 528-Byte Sector | "D"            | 1536~2047      | "H"                            | 2096~2111      |  |  |

Table 9: page organization in EDC units (x8)

| "A"area                  | "B"area                  | "C"area                  | "D"area                  | "E"area                  | "F"area                  | "G"area                  | "H"area                  |

|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| (1 <sup>st</sup> sector) | (2 <sup>nd</sup> sector) | (3 <sup>rd</sup> sector) | (4 <sup>th</sup> sector) | (1 <sup>st</sup> sector) | (2 <sup>nd</sup> sector) | (3 <sup>rd</sup> sector) | (4 <sup>th</sup> sector) |

| 256 words                | 256 words                | 256 words                | 256 words                | 8 words                  | 8 words                  | 8 words                  |                          |

Table 10: page organization in EDC units (x16)

| Sector                          | Main Field (C | olumn 0~1023)  | Spare Field (Column 1024~1055) |                |  |

|---------------------------------|---------------|----------------|--------------------------------|----------------|--|

| Sector                          | Area Name     | Column Address | Area Name                      | Column Address |  |

| 1 <sup>st</sup> 264-word Sector | "A"           | 0~255          | "E"                            | 1024~1031      |  |

| 2 <sup>nd</sup> 264-word Sector | "B"           | 256~511        | "F"                            | 1032~1039      |  |

| 3 <sup>rd</sup> 264-word Sector | "C"           | 512~767        | "G"                            | 1040~1047      |  |

| 4 <sup>th</sup> 264-word Sector | "D"           | 768~1023       | "H"                            | 1048~1055      |  |

Table 11: page organization in EDC units (x16)

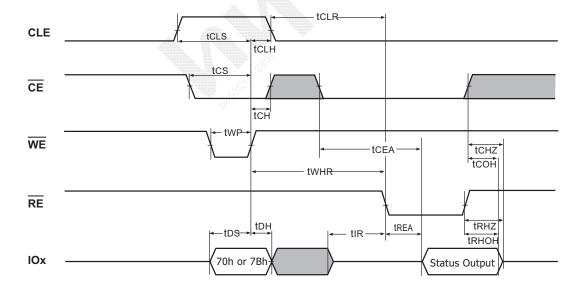

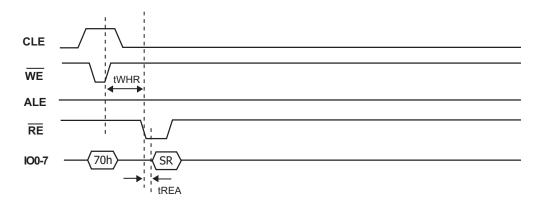

#### 3.11 Read Status Register.

The device contains a Status Register to retrieve the status value for the last operation issued. After writing 70h command to the command register, a read cycle outputs the content of the Status Register to the I/O pins on the falling edge of CE# or RE#, whichever occurs last. This two line control allows the system to poll the progress of each device in multiple memory connections even when RB# pins are common-wired. Refer to **Table 12** for specific Status Register definition, and to **Figure 10** and **Figure 38** for timings.

If Read Status register command is issued during multi-plane operations Read Status Register polling shall return the combined status value related to the outcome of the operation in the two planes according to this table:

| Status Register bit    | Composite status value |

|------------------------|------------------------|

| Bit 0, Pass/Fail       | OR                     |

| Bit 1, Cache Pass/Fail | OR                     |

Status register is dynamic in other words, user is not required to toggle RE# / CE# to update it.

The command register remains in Status Read mode until further commands are issued. Therefore, if the status register is read during a random read cycle, the read command (00h) should be given before starting read cycles.

#### Note:

Read Status Register command shall not be used for concurrent operations in of multi-dice stack configurations (single CE#). For this case, either "Read Status Enhanced" (**Section 3.12**) shall be used instead.

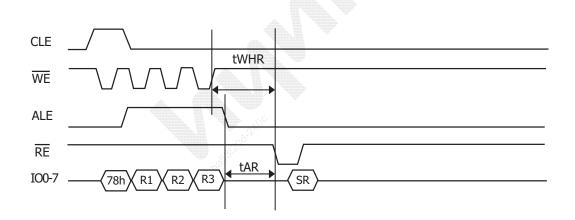

#### 3.12 Read Status Enhanced

Read Status Enhanced is an additional feature used to retrieve the status value for a previous operation in the following cases:

- on a specific die of a multi-dice stack configurations (single CE#), in case of concurrent operations

When 4Gbit dice are stacked(\*) to form 8Gbit DDP or 16Gbit QDP (single CE#), it is possible to run a first operation on the first 4Gbit, then activate a concurrent operation on the second (or third or fourth) device. (examples: Erase while Read, Read while Program, etc.)

- on a specific plane in case of multi-plane operations in the same die.

**Figure 39** defines the Read Status Enhanced behavior and timings. The plane and die address must be specified in the command sequence in order to retrieve the status of the die and the plane of interest.

Refer to **Table 12** for specific Status Register definition. The command register remains in Status Read mode until further commands are issued.

Status register is dynamic in other words, user is not required to toggle RE# / CE# to update it.

## 3.13 Read Status Register field definition

Table 12 below lists the meaning of each bit of Read Status Register and Read Status Enhanced

| 10 | Page<br>Program/<br>Page<br>Reprogram | Block<br>Erase   | Read             | Cache<br>Read    | Cache<br>Program/<br>Cache<br>reprogram | CODING                                       |

|----|---------------------------------------|------------------|------------------|------------------|-----------------------------------------|----------------------------------------------|

| 0  | Pass / Fail                           | Pass / Fail      | NA               | NA Pass / Fail   |                                         | N Page<br>Pass: '0' Fail: '1'                |

| 1  | NA                                    | NA               | NA               | NA               | Pass / Fail                             | N - Page<br>Pass: `0′ Fail: `1′              |

| 2  | NA                                    | NA               | NA               | NA               | NA                                      | -                                            |

| 3  | NA                                    | NA               | NA               | NA               | NA                                      | -                                            |

| 4  | NA                                    | NA               | NA               | NA               | NA                                      | -                                            |

| 5  | Ready / Busy                          | Ready / Busy     | Ready / Busy     | Ready / Busy     | Ready / Busy                            | Active: `0'<br>Idle: `1'                     |

| 6  | Ready / Busy                          | Ready / Busy     | Ready / Busy     | Ready / Busy     | Ready / Busy                            | Data cache Read/Busy<br>Busy: '0' Ready: '1' |

| 7  | Write<br>Protect                      | Write<br>Protect | Write<br>Protect | Write<br>Protect | Write<br>Protect                        | Protected: '0'<br>Not Protected: '1'         |

**Table 12: Status Register Coding**

## 3.14 Read EDC status register

This operation is available only in copy back program and it allows the detection of errors occurred during read for copy back. In case of multiple plane copy back, it is not possible to know which of the two read operation caused the error. After writing Read EDC status register command (7Bh) to the command register, a read cycle outputs the content of the EDC Register to the I/O pins on the falling edge of CE# or RE#, whichever occurs last.

Operation is same as read status register command. Refer to **Table 13** for specific EDC Register definitions:

| 10 | Copy back<br>program | CODING                            |

|----|----------------------|-----------------------------------|

| 0  | Pass / Fail          | Pass: '0' Fail: '1'               |

| 1  | EDC status           | No error: '0' Error: '1'          |

| 2  | EDC validity         | Invalid: '0' Valid: '1'           |

| 3  | NA                   | -                                 |

| 4  | NA                   | -                                 |

| 5  | Ready / Busy         | Busy: '0' Ready: '1'              |

| 6  | Ready / Busy         | Busy: '0' Ready: '1'              |

| 7  | Write Protect        | Protected: '0' Not Protected: '1' |

Table 13: EDC register coding

## 3.15 Reset

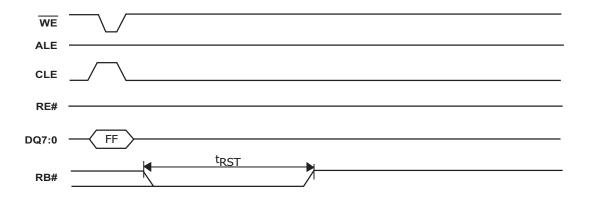

The device offers a reset feature, executed by writing FFh to the command register. If the device is in Busy state during random read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value E0h when WP# is high. Refer to **table 16** for device status after reset operation. If the device is already in reset state a new reset command will not be accepted by the command register. The RB# pin transitions to low for t<sub>RST</sub> after the Reset command is written. Refer to **Figure 28** for further details.

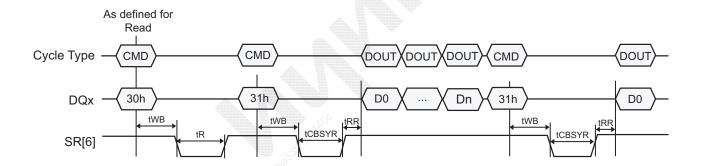

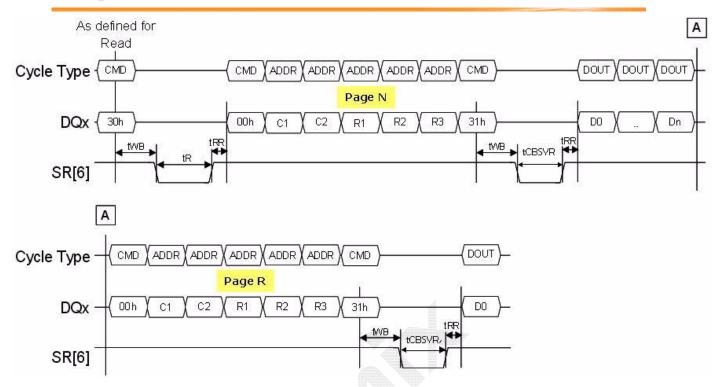

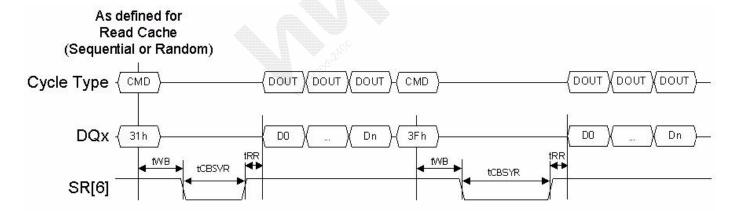

#### 3.16 Cache Read

Cache Read can be used to increase the read operation speed, as defined in **Section 3.1**, which is available only within a block. As soon as the user starts to read one page, the device automatically loads the next page into the cache register. Serial data output may be executed while data in the memory is read into cache register, Cache Read is initiated by the page read sequence (00-30h) on a page M.

After random access to the first page is complete (R/B# returned to high, or read status register IO<6> switches to high), two command sequences can be used to continue read cache:

- sequential read cache continue (command "31h" only): once the command is latched into the command register (see **Figure 30**), device does busy for a short time (t<sub>RCBSY</sub>), during which data of the first page is transferred from the data register to the cache register. At the end of this phase cache register data can be output by toggling RE# while the "next "page (page address M+1) is read from the memory array into data register.

- random read cache continue (sequence "00h" <page N address> "31"): once the command is latched into the command register (see **Figure 31**), device does busy for a short time ( $t_{RCBSY}$ ), during which data of the first page is transferred from the data register to the cache register. At the end of this phase cache register data can be output by toggling RE# while page N is read from the memory array into data register.

Subsequent pages are read by issuing additional "sequential" or "random" read cache continue command sequences. If serial data output time of one page exceeds random access time ( $t_R$ ), the random access time of the next page is hidden by data downloading of the previous page.

On the other hand, if 31h is issued prior to complete the random access to the next page, the device will stay busy as long as needed to complete random access to this page, transfer its contents into the cache register, and trigger the random access to the following page.

To terminate cache read, 3Fh command should be issued (see **Figure 32**). This command transfer data from data register to the cache register without issuing next page read.

During the Cache Read Operation, device doesn't allow any other command except for 31h, 3Fh, Read SR or reset (FFh). To carry out other operations Cache read must be ended either by 3Fh command or device must be reset by issuing FFh.

Read Status command (70h) may be issued to check the status of the different registers, and the busy/ready status of the cached read operations. More in detail:

- a) the Cache-Busy status bit I/O<6> indicates when the cache register is ready to output new data.

- b) the status bit I/O<5> can be used to determine when the cell reading of the current data register contents is complete.

#### Note:

31h and 3Fh commands reset the column counter thus when RE# is toggled to output the data of a given page, the first output data is related to the first byte of the page (column address 00h). Random data output command can be used to switch column address.

## 3.17 Cache Program

Cache Program is used to improve the program throughput by programing data using the cache register. The cache program operation can only be used within one block. The cache register allows new data to be input while the previous data that was transffered to the page buffer is programmed into the memory array. Cache program is available only within a block

After the serial data input command (80h) is loaded to the command register, followed by 5 cycles of address, a full or partial page of data is latched into the cache register.

Once the cache write command (15h) is loaded to the command register, the data in the cache register is transferred into the data register for cell programming. At this time the device remains in Busy state For a short time (tCBSYW). After all data of the cache register are transferred into the data register, the device returns to the Ready state, and allows loading the next data into the cache register through another cache program command sequence (80h-15h).

The Busy time following the first sequence 80h - 15h equals the time needed to transfer the data of cache register to the data register. Cell programming of the data of data register and loading of the next data into the cache register is conse quently processed through a pipeline model.

In case of any subsequent sequence 80h - 15h, transfer from the cache register to the data register is held off until cell programming of current data register contents is complete: till this moment the device will stay in a busy state (tCBSYW). Read Status commands (70h or 78h) may be issued to check the status of the different registers, and the pass/fail status of the cached program operations. More in detail:

- a) the Cache-Busy status bit I/O<6> indicates when the cache register is ready to accept new data.

- b) the status bit I/O<5> can be used to determine when the cell programming of the current data register contents is complete.

- c) the cache program error bit I/O<1> can be used to identify if the previous page (page N-1) has been successfully programmed or not in cache program operation. The latter can be polled upon I/O<6> status bit changing to "1".

- d) the error bit I/O<0> is used to identify if any error has been detected by the program / erase controller while program ming page N. The latter can be polled upon I/O<5> status bit changing to "1".

I/O<1> may be read together with I/O<0>.

If the system monitors the progress of the operation only with R/B#, the last page of the target program sequence must be programmed with Page Program Confirm command (10h). If the Cache Program command (15h) is used instead, the status bit I/O<5> must be polled to find out if the last programming is finished before starting any other operation.

See Table 12 and Figure 40 for more details.

## 3.18 Multi-plane Cache Program

The device supports multi-plane cache program, which enables high program throughput by programming two pages in parallel while exploiting the data and cache registers of both planes to implement cache. The device supports both the traditional and ONFI 1.0 command sets.

The command sequence can be summarized as follows:

- a) Serial Data Input command (80h), followed by the five cycle address inputs and then serial data for the 1<sup>st</sup> page. Ad dress for this page must be within 1<sup>st</sup> plane (A<20>=0). The data of 1<sup>st</sup> page other than those to be programmed do not need to be loaded. The device supports random data input exactly like page program operation.

- b) The Dummy Page Program Confirm command (11h) stops  $1^{st}$  page data input and the device becomes busy for a short time ( $t_{DBSY}$ ).

- c) Once device returns to ready again, 81h (or 80h) command must be issued, followed by  $2^{nd}$  page address (5 cycles) and its serial data input. Address for this page must be within  $2^{nd}$  plane (A<20>=1). The data of  $2^{nd}$  page other than those to be programmed do not need to be loaded.

- d) Cache Program confirm command (15h) Once the cache write command (15h) is loaded to the command register, the

data in the cache registers is transferred into the data registers for cell programming. At this time the device remains in Busy state for a short time (tCBSYW). After all data of the cache registers are transferred into the data registers, the device returns to the Ready state, and allows loading the next data into the cache register through another cache program command se quence.

The sequence 80h-...- 11h...-...15h (or the corresponding ONFI 80h-...- 11h...-...80h...-...15h ) can be iterated, and any new time the device will be busy for a for the tCBSYW time needed to complete cell programming of current data registers contents, and transfer from cache registers can be allowed.

The sequence to end multi-plane cache program is 80h-...- 11h...-...81h...-...10h (or 80h-...- 11h...-...80h...-...10h for the ONFI 1.0 case).

Figure 50 and Figure 51 show the command sequence for the multi plane cache program operation for the two protocols. Multi-plane Cache program is available only within two paired blocks belonging to the two planes..

User can check operation status by R/B# pin or read status register commands (70h or 78h)

If user opts for 70h, Status register read will provide a "global" information about the operation in the two planes. More in detail:

- a) I/O<6> indicates when both cache registers are ready to accept new data.

- b) I/O<5> indicates when the cell programming of the current data registers is complete

- c) I/O<1> identifies if the previous pages in both planes (pages N-1) have been successfully programmed or not. The latter can be polled upon I/O<6> status bit changing to "1".

- d) I/O<0> identifies if any error has been detected by the program / erase controller while programming the two pages N. The latter can be polled upon I/O<5> status bit changing to "1".

#### See Table 12 for more details

If the system monitor rs the progress of the operation only with R/B#, the last pages of the target program sequence must be programmed with Page Program Confirm command (10h). If the Cache Program command (15h) is used instead, the sta tus bit I/O<5> must be polled to find out if the last programming is finished before starting any other operation. Refer to **section 3.11** for further information.

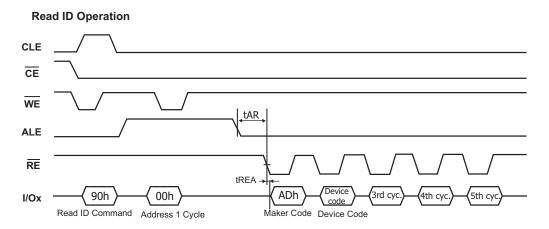

## 3.19 Read ID.

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of 00h.

The 5-byte Read ID configuration are supported: The device operating mode (5-byte) is selected through cam setting.

## 3.19.1 Legacy Read ID

Five read cycles sequentially output the manufacturer code (20h), and the device code and 3<sup>rd</sup>, 4<sup>th</sup>, and 5<sup>th</sup> cycle ID, respectively. The command register remains in Read ID mode until further commands are issued to it. **Figure 27** shows the operation sequence, while **Table 14** to **Table 18** explain the byte meaning. Complete read id code table is as follows.

| DENSITY | ORG | VCC  | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> | 4 <sup>th (1)</sup> | 5 <sup>th</sup> |

|---------|-----|------|-----------------|-----------------|-----------------|---------------------|-----------------|

|         | X8  | 3.0V | ADh             | DCh             | 90h             | 95h                 | 54h             |

| 4 Gbit  | X16 | 3.0V | ADh             | CCh             | 90h             | D5h                 | 54h             |

| 4 GDIC  | X8  | 1.8V | ADh             | ACh             | 90h             | 15h                 | 54h             |

|         | X16 | 1.8V | ADh             | BCh             | 90h             | 55h                 | 54h             |

|         | X8  | 3.0V | ADh             | D3h             | D1h             | 95h                 | 58h             |

| 8 Gbit  | X16 | 3.0V | ADh             | C3h             | D1h             | D5h                 | 58h             |

| DDP     | X8  | 1.8V | ADh             | A3h             | D1h             | 15h                 | 58h             |

|         | X16 | 1.8V | ADh             | B3h             | D1h             | 55h                 | 58h             |

|         | X8  | 3.0V | ADh             | D5h             | D2h             | 95h                 | 5Ch             |

| 16 Gbit | X16 | 3.0V | ADh             | C5h             | D2h             | D5h                 | 5Ch             |

| QDP     | X8  | 1.8V | ADh             | A5h             | D2h             | 15h                 | 5Ch             |

|         | X16 | 1.8V | ADh             | B5h             | D2h             | 55h                 | 5Ch             |

Table 14: Legacy " Read ID for supported configurations

NOTE: for 1.8V version, IO<7,3>=00 would mean "50nsec", while device serial cycle time is 45nsec

| DEVICE IDENTIFIER BYTE | DESCRIPTION                                     |

|------------------------|-------------------------------------------------|

| 1 <sup>st</sup>        | Manufacturer Code                               |

| 2 <sup>nd</sup>        | Device Identifier                               |

| 3 <sup>rd</sup>        | Internal chip number, cell type, etc.           |

| 4 <sup>th</sup>        | Page Size, Block Size, Spare Size, Organization |

| 5 <sup>th</sup>        | Multiplane information                          |

Table 15: "Legacy" Read ID bytes meaning

## 3<sup>rd</sup> ID Data

|                                                 | Description                                                   | I/07   | I/06   | I/05 I/04                                  | I/03 I/02                | I/O1 I/O0                |

|-------------------------------------------------|---------------------------------------------------------------|--------|--------|--------------------------------------------|--------------------------|--------------------------|

| Internal Chip Number                            | 1<br>2<br>4<br>8                                              |        |        |                                            |                          | 0 0<br>0 1<br>1 0<br>1 1 |

| Cell Type                                       | 2 Level Cell<br>4 Level Cell<br>8 Level Cell<br>16 Level Cell |        |        |                                            | 0 0<br>0 1<br>1 0<br>1 1 |                          |

| Number of<br>Simultaneously<br>Programmed Pages | 1<br>2<br>4<br>8                                              |        |        | 0 0<br>0 1<br>1 0<br>1 1                   |                          |                          |

| Interleave Program<br>Between multiple chips    | Not Support<br>Support                                        |        | 0<br>1 |                                            |                          |                          |

| Cache Program                                   | Not Support<br>Support                                        | 0<br>1 |        | , di<br>, di , di , di , di , di , di , di |                          |                          |

Table 16: Legacy Read ID 3<sup>rd</sup> byte description

## 4<sup>th</sup> ID Data

|                                    | Description                               | I/07             | I/06   | I/05             | I/04             | I/03             | I/02   | I/01             | I/O0             |

|------------------------------------|-------------------------------------------|------------------|--------|------------------|------------------|------------------|--------|------------------|------------------|

| Page Size<br>(w/o redundant area)  | 1KB<br>2KB<br>4KB<br>8KB                  |                  |        | 4                |                  |                  |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |

| Block Size<br>(w/o redundant area) | 64KB<br>128KB<br>256KB<br>512KB           | 143655100        | P      | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |        |                  |                  |

| Redundant Area Size (byte/512byte) | 8<br>16                                   |                  |        |                  |                  |                  | 0<br>1 |                  |                  |

| Organization                       | X8<br>X16                                 |                  | 0<br>1 |                  |                  |                  |        |                  |                  |

| Serial Access Minimum              | 50ns/30ns<br>25ns<br>Reserved<br>Reserved | 0<br>1<br>0<br>1 |        |                  |                  | 0<br>0<br>1<br>1 |        |                  |                  |

Table 17: Legacy Read ID 4th byte description

#### 5th ID Data

|                                    | Description                                                 | I/07 | I/06 I/05 I/04                                                       | I/03 I/02                | I/01 | I/O0 |

|------------------------------------|-------------------------------------------------------------|------|----------------------------------------------------------------------|--------------------------|------|------|

| Plane Number                       | 1<br>2<br>4<br>8                                            |      |                                                                      | 0 0<br>0 1<br>1 0<br>1 1 |      |      |

| Plane Size<br>(w/o redundant Area) | 64Mb<br>128Mb<br>256Mb<br>512Mb<br>1Gb<br>2Gb<br>4Gb<br>8Gb |      | 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0<br>1 1 1 |                          |      |      |

| Reserved                           |                                                             | 0    |                                                                      |                          | 0    | 0    |

Table 18: Legacy Read ID 5th byte description

## 3.20 Read ONFI Signature

To retrieve the ONFI signature, the command 90h together with an address of 20h shall be entered (i.e. it is not valid to enter an address of 00h and read 36 bytes to get the ONFI signature). The ONFI signature is the ASCII encoding of 'ONFI' where O' = AFH, O' = AF

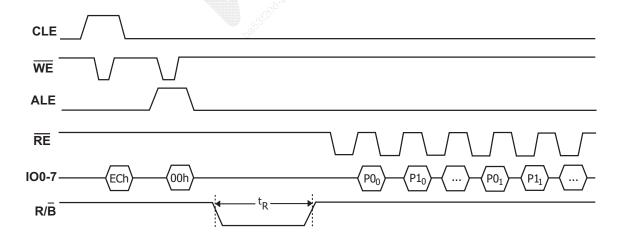

#### 3.21 Read Parameter Page

The Read Parameter Page function retrieves the data structure that describes the chip's organization, features, timings and other behavioral parameters. **Figure 37** defines the Read Parameter Page behavior.

This data structure enables the host processor to automatically recognize the Nand Flash configuration of a device. The whole data structure is repeated at leat three times.

The Random Data Read command can be issued during execution of the read parameter page to read specific portions of the parameter page.

The Read Status command may be used to check the status of read parameter page during execution. After completion of the Read Status command, 00h is issued by the host on the command line to continue with the data output flow for the Read Parameter Page command.