- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Checking Clock's configuration of IMX28

Hello everyone,

We are developing an application where we need to know well how the clock's should be configured in IMX28 processor.

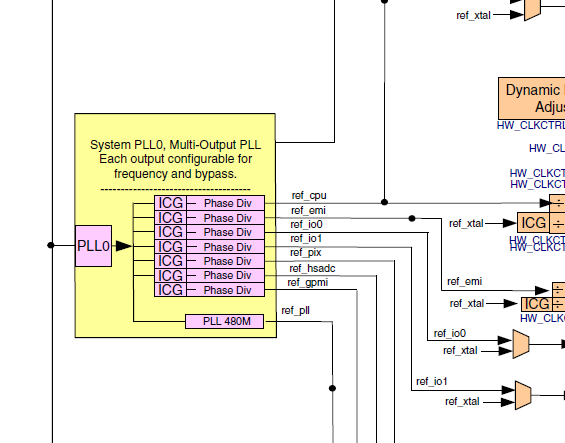

We have checked the Clock's diagram and we don't know how the " System PLL0, Multi-Output PLL" is configured or how configure it.

Our main question is: what is the value before each "ICG-PHASE DIV", and what is the output value of each output (ref_cpu,ref_emi,etc).

Could someone help us?

Thank you.

Hi Alexis

PLL0 is 480 MHz, as described in sect.10.8.1 System PLL0,

System/USB0 PLL Control Register 0 (HW_CLKCTRL_PLL0CTRL0) i.MX28 RM.

Examples of PLL configurations can be found in i.MX28 obds

Lab and Test Software (1)

"IMX_OBDS : On-Board Diagnostic Suit for the i.MX28"

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Igor,

Thank you for your reply, but we have already checked these sections and we haven't resolved our doubts. We still unknowing the behaviour inside the "System PLL0, Multi-Output PLL" and what value have the outputs ref_cpu, ref_emi, etc..

Thanks for everithing.