- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- Wireless Connectivity

- :

- Re: NT3H2211 I2C SRAM READ

NT3H2211 I2C SRAM READ

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NT3H2211 I2C SRAM READ

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Development Environment:

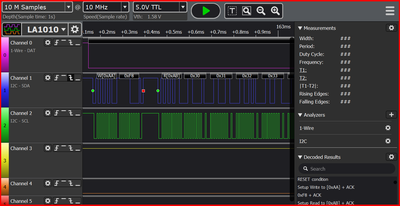

MPLABX/XC8/PIC18LF2580 connected to NT3H2211 via I2C.

I have followed the datasheet and have managed to get the

interface working. I can write and read all 64 bytes to SRAM.

A Logic analyzer has verified the commands, device addresses,

and data bytes (along with proper ACK's) are being xfer'ed as needed (to and from)

as indicated in the datasheet. The data sheet recommended delays have been

installed as instructed. Following the data sheet information exchange per

Section 9 - I2C COMMANDS Figure 18:

the first byte (D0) returned TO the HOST is indicated to be a DATA byte;

however, the SLAVE READ command byte (0xAB) is being returned in that

placeholder. The subsequent 15 bytes seem to be correct (and ordered correctly

albeit placed into the next array position - hopes this makes sense).

I have found to overcome this anomaly an extra read_device_byte() must

be placed after the write(0xab) command and before the loop to read all

SRAM page bytes. Is this behavior expected for all NT3H2211's? Is it a

chip batch specific problem? Or is it just this particular chip out of the

batch I have? Please advise.... Thanks for the assistance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hiii,

Do you have a picture or link to the board in question? GarageBand App

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

for ->debrawade

I do; however, I must ask: what is the nature of your inquiry?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

That must be a host issue, as the I2C wave looks good. It has the W(Device Add) - Register Add - R(Device Add)-Data0-…-DataN

Regards,

Ricardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Hope you are doing well. Could you please share a screenshot of what you see in the logical analyzer?

Best Regards,

Ricardo