- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

-

Hi, Vybrid expert:

the actual limitaion is ITU decoder, which can only output YUV422 or YUV444 (actually from YUV422).

so even we can input RGB888 and output RGB888, the quality will lost. right?

do we have anyway to do this without quality lost?

here is the information in our datasheet:

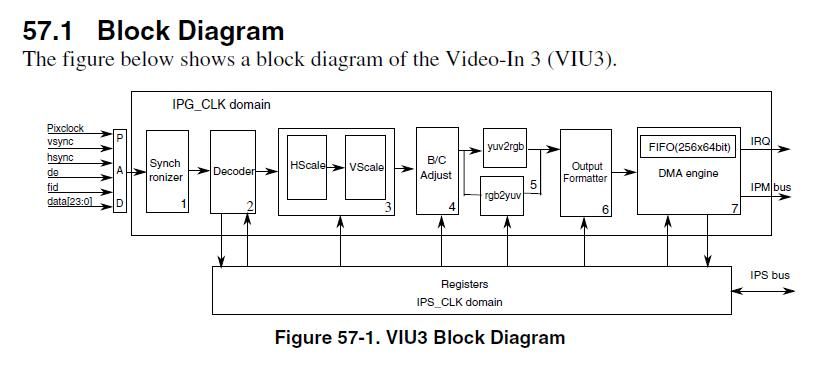

57.5.3 Decoder

The ITU Decoder block (2) detects the ITU656 timing reference signal (consists of a

four-word sequence in the following format: FF-00-00-XY) and extracts HSYNC,

VSYNC, field number signals and video data from the ITU data stream. The format of

active pixel data from the ITU stream is YUV 4:2:2. The decoder block can directly send

out this YUV 4:2:2 data, or interpolate it to YUV 4:4:4 format and send it out. This is

determined by the MODE444 field in the SCR register. This bit shall be set if the downscaler

is enabled, because the down-scaler works on YUV 4:4:4 data format.

已解决! 转到解答。

Skiping IOMUXC configuration, you need to set up just few registers like below. I have no hardware to verify RGB888 settings, hope it works.

VIU3->SCR = VIU3_SCR_MODE32BIT_MASK * 1 // 32 bit mode

| VIU3_SCR_ROUND_ON_MASK * 0

| VIU3_SCR_DITHER_ON_MASK * 0

| VIU3_SCR_DMA_ACT_MASK * 0

| VIU3_SCR_SCALER_EN_MASK * 0

| VIU3_SCR_YUV2RGB_EN_MASK * 0

| VIU3_SCR_BC_EN_MASK * 0

| VIU3_SCR_MODE444_MASK * 0 // YUV444 vs YUV422

| VIU3_SCR_ERROR_IRQ_MASK * 0

| VIU3_SCR_DMA_END_IRQ_MASK * 0

| VIU3_SCR_VSTART_IRQ_MASK * 0

| VIU3_SCR_HSYNC_IRQ_MASK * 0

| VIU3_SCR_VSYNC_IRQ_MASK * 0

| VIU3_SCR_FIELD_IRQ_MASK * 0

| VIU3_SCR_ECC_EN_MASK * 0

| VIU3_SCR_ERROR_EN_MASK * 0

| VIU3_SCR_DMA_END_EN_MASK * 0

| VIU3_SCR_VSTART_EN_MASK * 0

| VIU3_SCR_HSYNC_EN_MASK * 0

| VIU3_SCR_VSYNC_EN_MASK * 0

| VIU3_SCR_FIELD_EN_MASK * 0

| VIU3_SCR_FORMAT_CTRL_MASK * 0 // replace 0 with required RGB888 byte order setting

| VIU3_SCR_SOFT_RESET_MASK * 0

;

VIU3->DMA_ADDR = VIDEO_BASE; // address to store image data

VIU3->DMA_INC = 0; // 0 - noninterlaced

VIU3->EXT_CONFIG = VIU3_EXT_CONFIG_CS_EN_MASK * 0 // chroma swap enable=1

| VIU3_EXT_CONFIG_LENDIAN_MASK * 0 // little endian=1

| VIU3_EXT_CONFIG_RGB2YUV_EN_MASK * 0 // RGB->YUV conversion enable=1

| VIU3_EXT_CONFIG_DE_VALID_MASK * 0 //

| (4 << 5) // input format=4 - parallel RGB888, input format=5 - 8bit serial RGB888

| VIU3_EXT_CONFIG_PCLK_POL_MASK * 1 // pixel clock polarity

| VIU3_EXT_CONFIG_VSYNC_POL_MASK * 1 // VSYNC polarity

| VIU3_EXT_CONFIG_HSYNC_POL_MASK * 1 // HSYNC polarity

| VIU3_EXT_CONFIG_DE_POL_MASK * 0 // DE polarity

| VIU3_EXT_CONFIG_HMIRROR_EN_MASK * 0 // horizontal mirror enable

;

// enable VSYNC interrupt

VIU3->SCR |= VIU3_SCR_VSYNC_EN_MASK | VIU3_SCR_VSYNC_IRQ_MASK ;

//VSYNC ISR

void vsyncISR(void)

{

VIU3->SCR |= VIU3_SCR_DMA_ACT_MASK; // clear interrupt flags and start new DMA cycle

}

Weisong,

VIU3 supports two ITU input modes, four RGB input modes and one parallel YUV input mode, see 57.3 Video Input Signal Mapping. ITU decoder block is used for ITU input mode. No quality is lost, unless you tell VIU3 to convert RGB888 to different formats.

Skiping IOMUXC configuration, you need to set up just few registers like below. I have no hardware to verify RGB888 settings, hope it works.

VIU3->SCR = VIU3_SCR_MODE32BIT_MASK * 1 // 32 bit mode

| VIU3_SCR_ROUND_ON_MASK * 0

| VIU3_SCR_DITHER_ON_MASK * 0

| VIU3_SCR_DMA_ACT_MASK * 0

| VIU3_SCR_SCALER_EN_MASK * 0

| VIU3_SCR_YUV2RGB_EN_MASK * 0

| VIU3_SCR_BC_EN_MASK * 0

| VIU3_SCR_MODE444_MASK * 0 // YUV444 vs YUV422

| VIU3_SCR_ERROR_IRQ_MASK * 0

| VIU3_SCR_DMA_END_IRQ_MASK * 0

| VIU3_SCR_VSTART_IRQ_MASK * 0

| VIU3_SCR_HSYNC_IRQ_MASK * 0

| VIU3_SCR_VSYNC_IRQ_MASK * 0

| VIU3_SCR_FIELD_IRQ_MASK * 0

| VIU3_SCR_ECC_EN_MASK * 0

| VIU3_SCR_ERROR_EN_MASK * 0

| VIU3_SCR_DMA_END_EN_MASK * 0

| VIU3_SCR_VSTART_EN_MASK * 0

| VIU3_SCR_HSYNC_EN_MASK * 0

| VIU3_SCR_VSYNC_EN_MASK * 0

| VIU3_SCR_FIELD_EN_MASK * 0

| VIU3_SCR_FORMAT_CTRL_MASK * 0 // replace 0 with required RGB888 byte order setting

| VIU3_SCR_SOFT_RESET_MASK * 0

;

VIU3->DMA_ADDR = VIDEO_BASE; // address to store image data

VIU3->DMA_INC = 0; // 0 - noninterlaced

VIU3->EXT_CONFIG = VIU3_EXT_CONFIG_CS_EN_MASK * 0 // chroma swap enable=1

| VIU3_EXT_CONFIG_LENDIAN_MASK * 0 // little endian=1

| VIU3_EXT_CONFIG_RGB2YUV_EN_MASK * 0 // RGB->YUV conversion enable=1

| VIU3_EXT_CONFIG_DE_VALID_MASK * 0 //

| (4 << 5) // input format=4 - parallel RGB888, input format=5 - 8bit serial RGB888

| VIU3_EXT_CONFIG_PCLK_POL_MASK * 1 // pixel clock polarity

| VIU3_EXT_CONFIG_VSYNC_POL_MASK * 1 // VSYNC polarity

| VIU3_EXT_CONFIG_HSYNC_POL_MASK * 1 // HSYNC polarity

| VIU3_EXT_CONFIG_DE_POL_MASK * 0 // DE polarity

| VIU3_EXT_CONFIG_HMIRROR_EN_MASK * 0 // horizontal mirror enable

;

// enable VSYNC interrupt

VIU3->SCR |= VIU3_SCR_VSYNC_EN_MASK | VIU3_SCR_VSYNC_IRQ_MASK ;

//VSYNC ISR

void vsyncISR(void)

{

VIU3->SCR |= VIU3_SCR_DMA_ACT_MASK; // clear interrupt flags and start new DMA cycle

}

Hi, Edward

thanks for your information.

but how to explain the following information: ( I think the ITU decoder has limitation no matter the input are RGB888 or others.)

The format of active pixel data from the ITU stream is YUV 4:2:2. The decoder block can directly send

out this YUV 4:2:2 data, or interpolate it to YUV 4:4:4 format and send it out.