- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- Re: Determining T1042 timebase frequency

Determining T1042 timebase frequency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Determining T1042 timebase frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Everyone,

We are trying to determine the right frequency at which the timebase is updated.

According to the reference manual the core timebase frequency is calculated as follows :

Timebase clock = (platform_clock/16) / TBCLKDIVR

in our case :

- Platform clock is 600 Mhz

- RCPM_PCTBCKSELR is 0 -> Core Timebase is clocked with Platform Clock /16

- TBCLKDIVR is 0x2 -> 1/8

so our timebase frequency should be : 600/(16*8) = 4.6875 Mhz

but when measuring with the logic analyzer we get a timebase frequency of 50Mhz.

I would like to confirm if I a calculated the right frequency or if I missed something,

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The only pin available to me was the UART_SOUT which I had to configure as GPIO1[15] by modifying the RCW.

I used the debugger RCW override function to use my new RCW, I figured out that the debugger will set the platform PLL to 4:1 even though my RCW is setting it to be 6:1. meaning that my platform clock is 400 Mhz and not 600 Mhz (SYSCLK is 100Mhz).

which make a little bit more sense, if we consider that platform clock is only divided by TBCLKDIVR, 400Mhz/8 = 50 Mhz

I think that "RCPM_PCTBCKSELR is 0 -> Core Timebase is clocked with Platform Clock /16" statement is not true.

Can you please confirm.

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You wrote:

> when measuring with the logic analyzer we get a timebase frequency of 50Mhz

How exactly you did that?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply,

I did set the decrementer to a value of 50000 ticks

with Auto reload enabled (TCR= 0x0000000000400000)

then in the decrementer exception vector (IVOR10) I toggle a GPIO which I measure with the logic analyzer.

I get a frequency of 1Khz (a period of 1 ms)

which makes me believe I am running at 50 Mhz (50000 * 1Khz)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

DECAR in your case is zero.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The debugger can't read it (according to core manual "The DECAR contents cannot be read")

but I know that I wrote the right value and I am getting decremented exceptions at a fixed interval.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

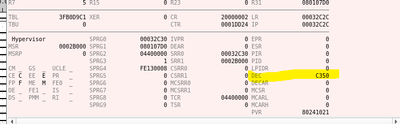

Please show using Trace32 values of:

RCPM_PCTBCKSELR

RCPM_TBCLKDIVR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is a screenshot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

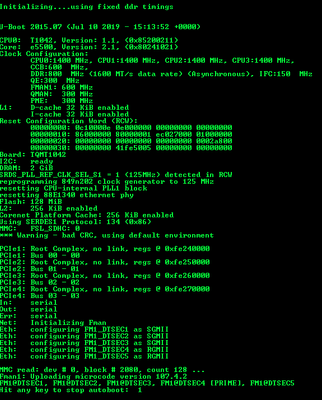

What is SYSCLK frequency?

Please provide U-Boot booting log.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The system frequency is 100MHz

here is the u-boot log

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

600/50=12

I have no idea how such ratio can be obtained.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please combine all consistent experimental data into single Word or PDF document.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

just making sure, you want me to describe the issue with relevant data/screenshots and post it here ?

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, please.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ufedor , just following up on this.

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your understanding is correct.

Time base frequency = (Platform clock )/RCPM_TBCLKDIVR When RCPM_PCTBCKSELR [PCTBCKSELn] = 0, Core Timebase is clocked with Platform Clock/ RCPM_TBCLKDIVR [tbclkdiv].

It is recommended to have the default value of RCPM_TBCLKDIVR [tbclkdiv], i.e., 0x00 : 1/16. This field should not be modified by customer as all the testing are done with Timebase clock divider configuration = 1/16.

Comment is added in T1042RM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you,

But then we have another problem, the erratum A-010651 states that the workaround is changing the RCPM_TBCLKDIVR [tbclkdiv], to 0x08 : 1/32.

but you mentioned we should not change it. how can we workaround this errata then ?

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the quick replies,

as I mentioned in an earlier comment, I found out that using the temporary RCW has set my PLL ration to 4:1 so I was running at 400Mhz when I got 50Mhz.

Now after setting back the platform clock to 600Mhz I measure a time base frequency of 75Mhz. (600/8)

which makes me believe that the user manual is wrong