- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello all

I am using s32k142 EVB and configure the clock to run in HSRUN mode and I want to be sure that the clock output is correct but I found that It is not correct. I am using the internal oscillator not the external.

if the s32k142 doesn't have external oscillator on the board?

If I use wrong test please tell me the correct test to be sure that:

- configure the HSRUN mode with :

- SPLL = 112 MHz

- Core & System clocks = 112 MHz (their input must be the SPPL)

- Bus clock = 56 MHz

and I will attach the code to test the clock please help me in this issue

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I don't think it's wrong. The output 112MHz signal may be too high frequency. In addition, the oscilloscope bandwidth of 350MHz may be too low.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi RehabSoliman,

I am using s32k142 EVB and configure the clock to run in HSRUN mode and I want to be sure that the clock output is correct but I found that It is not correct.

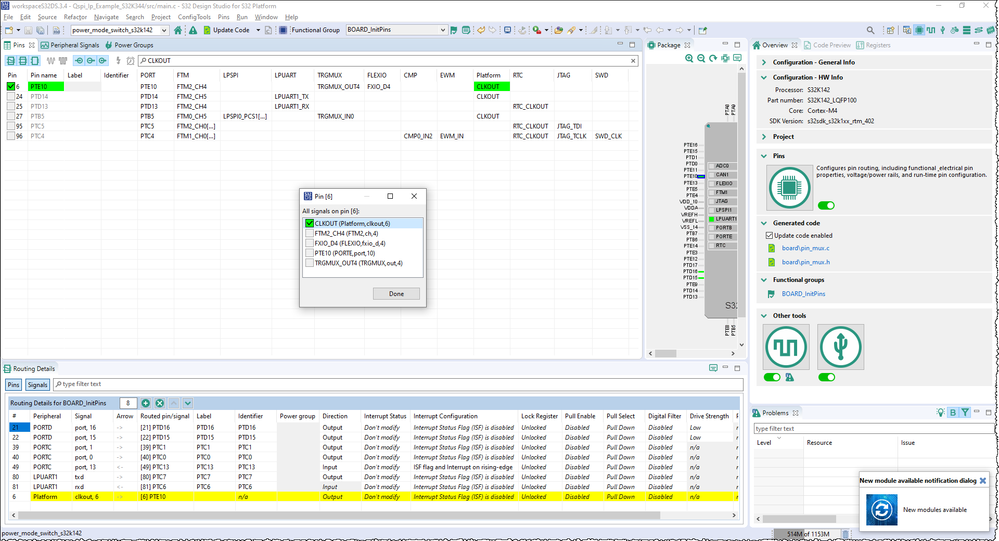

The method of flipping IO is imprecise. SCG_CLKOUTCNFG[CLKOUTSEL] and SCG_CLKOUTCNFG[CLKOUTSEL] can output clock on the CLKOUT pin.(Do not forget select the CLKOUT in pins tool)

I am using the internal oscillator not the external.

But the clock_configuration.png shows that you select external 8MHz crystal as input of SPLL_VCO.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your reply

but I mean I want to be sure that the frequency is 112MHz so I need a way to test this part.

I want to Check system clock speed (main clock speed) is 112MHz

is the s32k142EVB has external oscillator on the board?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

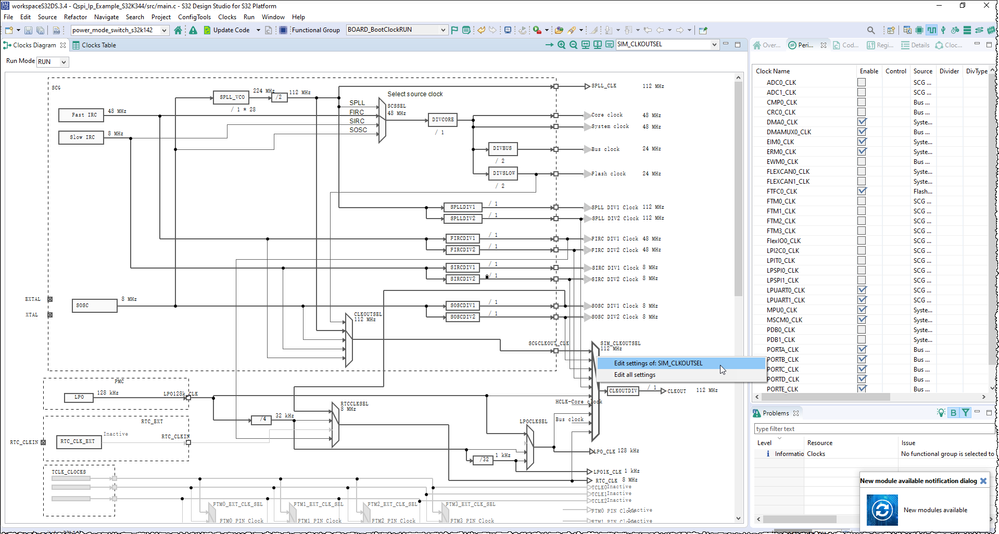

Did you output the clock by refer SCG_CLKOUTCNFG[CLKOUTSEL] SPLL_CLK.png? What is the frequency measured by the oscilloscope on the CLKOUT pin?

S32k142EVB has external 8MHz crystal on the board, just like the project configured.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

the clock out is 112MHz

but I want to be sure that the core clock and system clock is 112MHz

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Did you tried to select HCLK output CORE_CLK?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

No, I didn't because I don't know how to this

could you tell me the steps and I will try to do ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This way you can output SPLL_CLK at CLKOUT pin.

the clock out is 112MHz

I am not sure if you achieve it(output SPLL_CLK at CLKOUT pin). Did you select which pin as CLKOUT? Are you able to measure the frequency by using oscilloscope?)

The method is the same, edit settings of SIM_CLKOUTSEL and select HCLK.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I did this test and the spll is 112MHZ but I want to be sure that the core clock has 112MHz not 48MHz

could you help me in this part?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

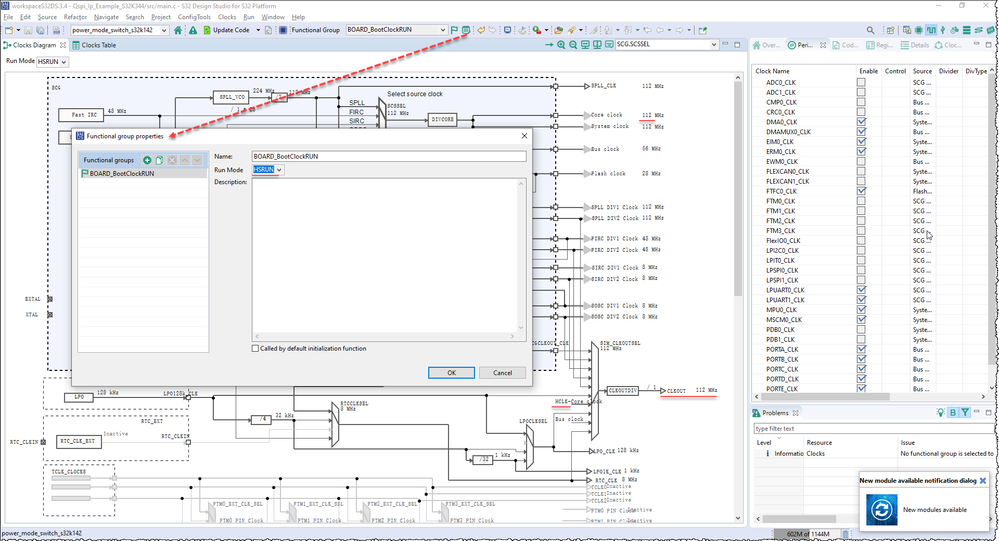

I did not configure the Core to 112 MHz in last reply, so even if I choose CLKOUT that image shows 48MHz. I'm not sure if you have modified the core frequency to 112MHz, what is the frequency of CLKOUT output by the oscilloscope now?

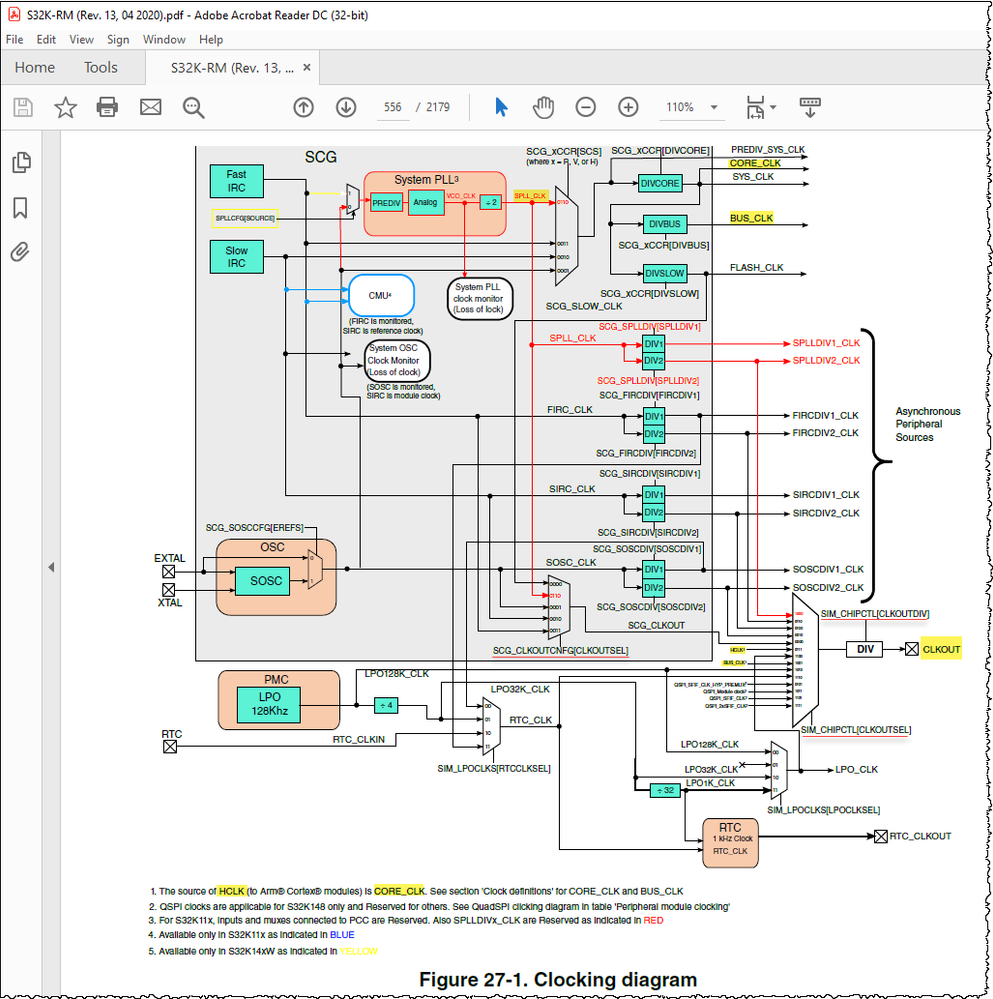

In below image, you can see the core clock is configure to 112MHz and the CLKOUT(HCLK selected) will be 112MHz. I am not sure if you notice the note1 in Figure 27-1. Clocking diagram: 1. The source of HCLK (to Arm® Cortex® modules) is CORE_CLK.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I don't think it's wrong. The output 112MHz signal may be too high frequency. In addition, the oscilloscope bandwidth of 350MHz may be too low.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

thanks for your support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I want to know is it mandatory to use power manager when I want to set the HSRUN mode

or it is not related because if I turn the power manager the HSRUN mode not work

![SCG_CLKOUTCNFG[CLKOUTSEL] SPLL_CLK.png SCG_CLKOUTCNFG[CLKOUTSEL] SPLL_CLK.png](https://community.nxp.com/t5/image/serverpage/image-id/190799iCDC580114A797353/image-size/large?v=v2&px=999)

![SCG_CLKOUTCNFG[CLKOUTSEL] SPLL_CLK.png SCG_CLKOUTCNFG[CLKOUTSEL] SPLL_CLK.png](/t5/image/serverpage/image-id/190848i157FE8B96A433ADC/image-size/large?v=v2&px=999)