- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: WatchDog reset Issues with S32DS 2018.R1 build id 180815

WatchDog reset Issues with S32DS 2018.R1 build id 180815

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

WatchDog reset Issues with S32DS 2018.R1 build id 180815

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

I'd implemented a watchdog code on the S32K142 device where I checked & it's working absolutely fine. I developed with 300ms watchdog timeout & refreshing at 10ms rate.

Strangely, during the modifications in the later software, just adding accessing a variable in the main code is causing the reset and that too immediately 100ms after initializing, not at 300ms. I'm currently using S32DS version 2018.R1 & Build id: 180815 as shown below.

Also, this strange reset is not happening with the other system where the version is 2018.R1 & build id is 180326 as shown below.

I would like to know the probable reasons for the same.

Thanks in advance,

Raju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

two ideas from my side:

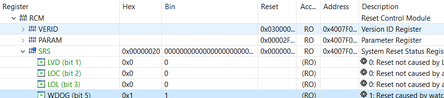

- did you confirmed in register RCM_SRS that the reset really comes from watchdog?

- if some problems appears after adding one instruction or variable or something like that, I would try to disable optimizations for test purposes (screenshot attached).

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

Thanks for the response.

- Yes, I checked the RCM_SRS and it confirms that the reset is happening because of the Watchdog.

-Also, My Optimization is none as well.

One thing I observed was I'm not enabling & disabling the interrupts during the refresh mechanism. If I do that the reset is not occurring.

Does the interrupts making the watchdog reset like this, kindly clarify the below points

- Why accessing the variable is causing the reset

- Would like to know what does the interrupt mean to the watchdog refresh mechanism

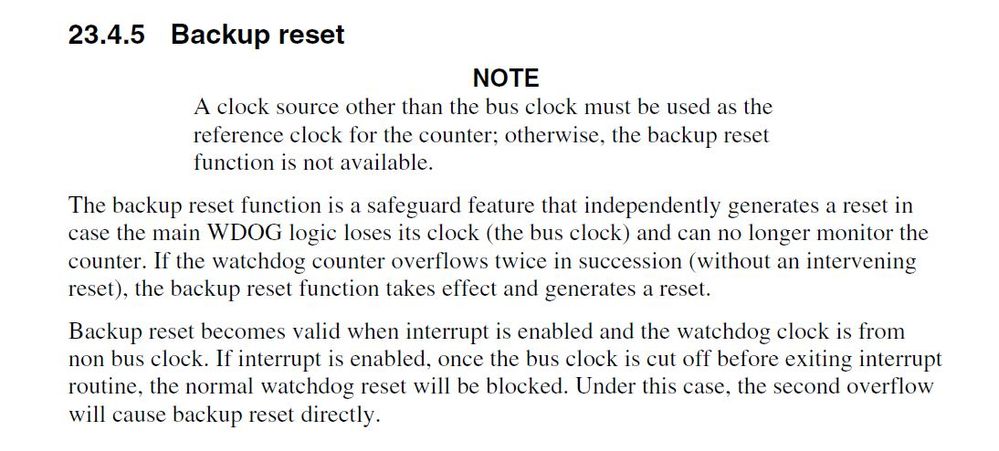

- I also saw backup reset mechanism for the Watchdog feature, but the software was not enabled with an interrupt also it is happening immediately after 100ms where my watchdog timer is 300ms.

Kindly clarify in this regard,

Thanks in advance,

Raju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raju,

accessing of variable or interrupts have nothing to do with watchdog. That seems to be just a side effect.

One idea - I would try to enable watchdog interrupt (INT bit in CS register) and disable watchdog in debug mode (DBG bit in CS). Once the interrupt is triggered, check the watchdog registers if you see anything unusual (CNT, TOVAL values...).

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

Thanks for the support & valuable suggestion.

I enabled the WDOG_EWM_IRQn both in the initialization and NVIC configuration. There is a reset because where the RCM-> SRS shows it is because of WDOG, but it did not cause any WDOG_EWM_IRQn though I kept a breakpoint at WDOG_EWM_IRQn.

Also, as I told the reset occurs after 100ms which may be the reason why the watch there is no WDOG_EWM_IRQn.

Then in such a case, what are the other causes for WDOG reset other than time/ TOVAL count. Also, during this time there is a refresh tick is happening every 10ms.

Looking forward to your valuable support.

Thanks & Regards,

Raju

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raju,

after some deeper investigation, it seems it's really necessary to disable interrupts during refresh. You wrote:

"One thing I observed was I'm not enabling & disabling the interrupts during the refresh mechanism. If I do that the reset is not occurring."

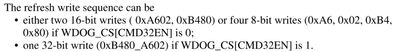

But there's a note in the RM:

"Before starting the refresh sequence, disable the global

interrupts. Otherwise, an interrupt could effectively invalidate

the refresh sequence, if the interrupt occurs before the refresh

writes finish. After the sequence finishes, restore the global

interrupt control state."

And there's also code example:

To refresh the watchdog and reset the watchdog counter to zero, a refresh sequence is

required. The code snippet below shows an example for 32-bit write.

DisableInterrupts; // disable global interrupt

WDOG_CNT = 0xB480A602; // refresh watchdog

EnableInterrupts; // enable global interrupt

So, if this works, I would stick to this solution.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

Thanks for the valuable information.

But, the reset is happening immediately after 100ms where the watchdog configuration is 300ms. Also, I can confirm there is a refresh at the 10ms rate. I would like to know whether the interrupts during the refresh mechanism reset the device else just ignores or invalidates the refresh mechanism.

Kindly confirm the same.

Raju

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raju,

could you show me configuration of watchdog registers? And do you use 32bit write for refreshing? Or?

I'm not sure about the reason, I will ask apps/design team. But need more details...

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

Thanks for the response again.

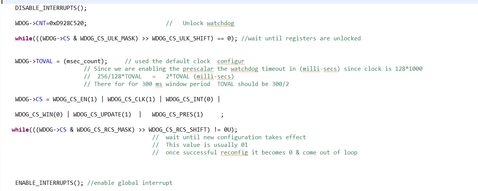

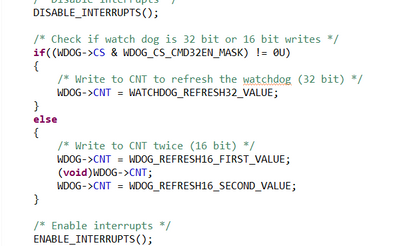

My WatchDog Configuration is as shown below.

My refresh Configuration is as shown below.

Let me know where I'm going wrong. Looking forward for your valuable response.

Thanks in advance.

RAJU.