- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hello,

I'm using spi_pal demo from SDK S32DS_ARM_v2018.R1.

The master is configured to use FLEXIO SPI.

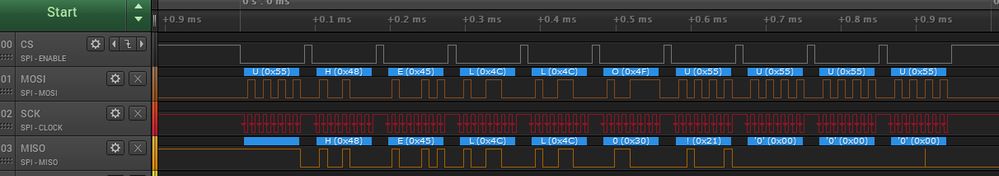

I have a question related to the CS pin. As you can see on the picture below, the CS is disabled between every bytes.

Is there a way to enable the CS pin as long as the master has data to transmit?

I looked into the FLEX SPI driver but I'm not familliar with it.

From Master side (running on another S32k148EVB board), it seems that the LPSPI IRQ is not triggered when the CS is enabled/disabled. I tryed to confirgure the interrupt on PTB0 using INT_SYS_EnableIRQ and INT_SYS_InstallHandler but it seems that it's never triggered.

Aslo the lpspi Callback is not triggered when the CS pin status change.

已解决! 转到解答。

Hi,

This feature is not available in Flexio, but you can use it on LPSPI. Please switch to LPSPI and select continuous mode.

In this mode CS is assert for all frames which are configured in your sending function.

I don't get exactly what are you trying to do with with the next SPI. Why both of them are masters?

If PTB0 is routed to Flexio you can't use it as GPIO.

Best regards,

Razvan

Hi,

This feature is not available in Flexio, but you can use it on LPSPI. Please switch to LPSPI and select continuous mode.

In this mode CS is assert for all frames which are configured in your sending function.

I don't get exactly what are you trying to do with with the next SPI. Why both of them are masters?

If PTB0 is routed to Flexio you can't use it as GPIO.

Best regards,

Razvan

Hi, Razvan-nicolae,

I noticed the S32K1xx RM Chapter 52.5.3" For CPHA=1, the select can remain asserted for multiple transfers and the timer status flag can be used to indicate the end of the transfer." Does it mean that it can enable the CS pin as long as the master has data to transmit? If not, what does it mean?

Thanks, BR,

Han