- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Oscillator and SPLL guidelines S32K144

03-08-2018

12:38 PM

1,525 次查看

christofferjärl

Contributor II

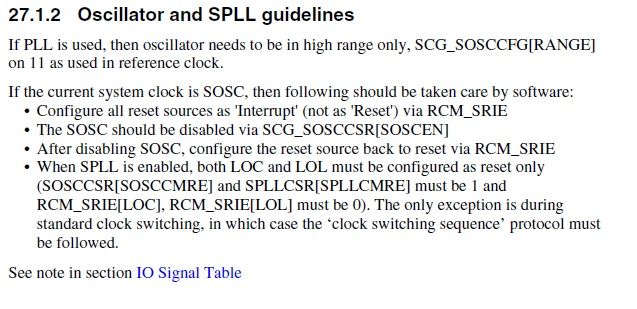

I have been going through the RM to understand and read about clocks.

But one thing i don't get is:

I can't see any of this applied in the examples using SOSC and SPLL (clocks_and_modes.c)

When does this apply? Is it not important?

2 回复数

04-10-2020

01:21 AM

1,316 次查看

carmelo_salva

Contributor I

Hi,

I've a question regarding the topic.

Since I'm using 8 MHz externl crystal, I've configured the SCG_SOSCCFG[RANGE] = 10 (Medium frequency range selected for the crystal oscillator of 4 MHz to 8 MHz) even if the SPLL is selected as reference clock (SCG_RCCR[SCS] = 6 System PLL).

Every seems to work correctly.

What are the possible side-effect?

Is it a wrong configuration for RM 28.1.2?

Regards,

Carmelo

03-12-2018

03:54 AM

1,316 次查看

NXP TechSupport

Hi Chris,

Please follow the reference manual.

The examples are rather simple.

Regards,

Daniel