- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- ソフトウェア・フォーラム

- :

- S32 デザインスタジオ

- :

- Issue with Pin and clock Configuration for S32K146 using SDK_3.0RTM

Issue with Pin and clock Configuration for S32K146 using SDK_3.0RTM

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Issue with Pin and clock Configuration for S32K146 using SDK_3.0RTM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

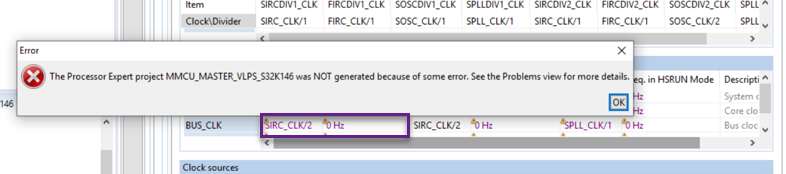

We are generating code through processor expert for S32K146 SDK ver.3.0.0 RTM. We facing below issues,

1.Not able to generate pin configuration for some of the random pins.

2.Facing issue while disabling clocks for VLPS mode.

please find attached screen shots(PE_VLPS.png and PE_VLPS1.png) and guide for the same.

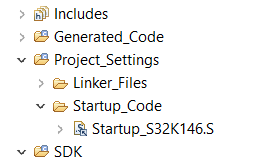

3.Also not able to generate "startup_S32K146.s" startup file.Is there any settings needs to do?

Please find attachment(Startup_File.png).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You need to fix all the errors in you configuration first.

For example:

You cannot select SIRC as the clock source, if SIRC is disabled (0Hz).

Also, the SDK RTM 3.0.x driver (POWER_SYS_SetMode(VLPS, POWER_MANAGER_POLICY_AGREEMENT) function) switches the system clock to SIRC automatically before the MCU enters the VLPS mode.

You can step the code a watch registers.

The Startup_S32K146.s file is in this folder:

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Daniel Martynek for your valuable reply.