- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- PLL & mc9s12xdt512

PLL & mc9s12xdt512

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

I am going to use to mc9s12xdt512 without PLL support.

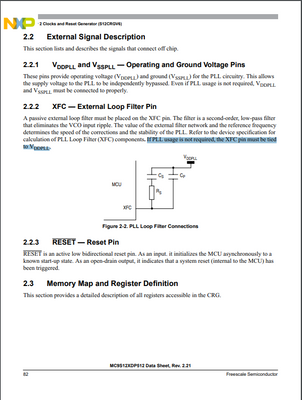

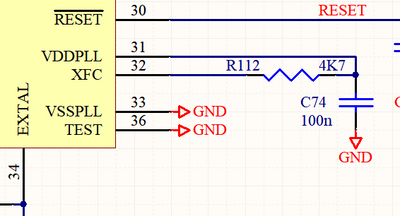

The manual mensions that "If PLL usage is not required, the XFC pin must be tied

to VDDPLL."

The same reference is made for mc9s12dg256. In a forum discussion a few years ago, it turned out that this was an error in the document and that the XFC pin must be connected to VDDPLL via a 4K7 resistor.

I assume that in the case of the mc9s12xdt512 it is also an error in the document and that in the mc9s12xdt512 the XFC pin must also be connected to VDDPLL via a 4K7 resistor.

Can anyone confirm this?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have found an answer I provided in 2010 after discussion with the design team. Both solutions are OK....but...

"

The reason why this resistor is recommended is that we want to avoid that the XFC input goes to too low value. When the PLL is off, it would not matter since XFC is internally pulled to VDDPLL. However we do release the XFC just after reset (because the PLL is enabled and tries to multiply the oscillator up). In this short phase until the software turns the PLL down again, XFC voltage could collapse (the chargepump could pull it down pretty easy against no load on the board), such the VCO may go to very high frequency. If in this case a clock monitor event would happen (or even the lock sensor might be misleaded), the high frequency of the VCO could adversely affect the operation of the mcu.

You see the if, if, if so it is not too likely that actually bad things may happen, but it is not totally bullet proof either. That's why a resistor or even a short to VDDPLL is recommended.

"

Best regards,

Ladislav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have found an answer I provided in 2010 after discussion with the design team. Both solutions are OK....but...

"

The reason why this resistor is recommended is that we want to avoid that the XFC input goes to too low value. When the PLL is off, it would not matter since XFC is internally pulled to VDDPLL. However we do release the XFC just after reset (because the PLL is enabled and tries to multiply the oscillator up). In this short phase until the software turns the PLL down again, XFC voltage could collapse (the chargepump could pull it down pretty easy against no load on the board), such the VCO may go to very high frequency. If in this case a clock monitor event would happen (or even the lock sensor might be misleaded), the high frequency of the VCO could adversely affect the operation of the mcu.

You see the if, if, if so it is not too likely that actually bad things may happen, but it is not totally bullet proof either. That's why a resistor or even a short to VDDPLL is recommended.

"

Best regards,

Ladislav