- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Re: How to get SCI 7 to send data.

How to get SCI 7 to send data.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

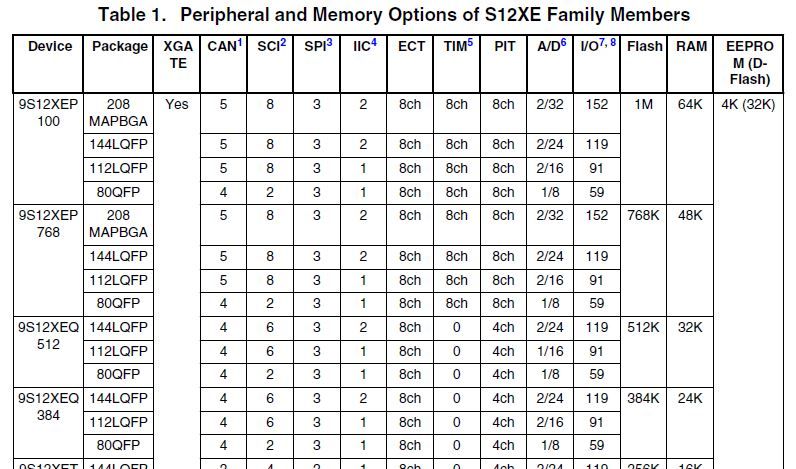

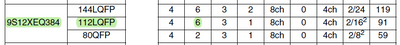

I am using MC9s12XEQ384 in 112 pin package.

I can send data on SCI0, SCI4 and SCI5. But SCI7 looks like it is not initialised.

This is what my initialisation looks like :

SPI0CR1 = 0; // Disable SPI

SPI1CR1 = 0;

SPI2CR1 = 0;

PTLRR = 0; // Port L route register

SCI7SR2 = 0x00; // AMAP = 0x80;

SCI0BD = Baud115200; // Fast Baud.

SCI4BD = Baud115200; // Load SCIxBDH and SCIxBDL registers

SCI5BD = Baud115200;

SCI6BD = Baud115200;

SCI7BD = Baud115200;

SCI0CR1 = 0; // 1 Start, 8 Data, 1 Stop bits. Parity disabled

SCI4CR1 = 0;

SCI5CR1 = 0;

SCI6CR1 = 0;

SCI7CR1 = 0;

SCI0CR2 = RE | TE; // Enable Receiver & Transmitter

// The transmit interrupt is setup when there is data to send

SCI4CR2 = RE | TE;

SCI5CR2 = RE | TE;

SCI6CR2 = RE | TE;

SCI7CR2 = RE | TE;

I am sending data as follows :

if ((SCI7SR1 & TDRE) != 0) // Transmit data register empty

SCI7DRL = 0x55;

if ((SCI6SR1 & TDRE) != 0) //

SCI6DRL = 0x55;

if ((SCI4SR1 & TDRE) != 0) //

SCI4DRL = 0xaa;

if ((SCI5SR1 & TDRE) != 0) //

SCI5DRL = 0xaa;

if ((SCI0SR1 & TDRE) != 0) //

SCI0DRL = 0x55;

The TDRE bit in SCI7SR1 is never set.

Which to points to initialisation.

What am I missing?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think I have found it.

My processor does not have SCI 6 and 7

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does someone have Processor Expert ?

I would like to see how it initialises SCI0 and SCI7.

I can get SCI0, 4 and 5 to initialise and to send data.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, you are right.

As you can see in Table D-2 of Ref Manual: https://www.nxp.com/docs/en/data-sheet/MC9S12XEP100RMV1.pdf

And pinout explanation:

- Versions with 6 SCI modules will have SCI0, SCI1, SCI2, SCI3, SCI4 and SCI5.

So you can use only 6 SCI modules.