- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- CodeWarrior startup routine and S12Z ECC RAM initialization

CodeWarrior startup routine and S12Z ECC RAM initialization

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CodeWarrior startup routine and S12Z ECC RAM initialization

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

After migration from Freescale to NXP it became unclear were to report bugs or concerns. Is Community really right place for this?

ECCSTAT RDY bit explanation from S12ZVC RM:

ECC Ready— Shows the status of the ECC module.

0 Internal SRAM initialization is ongoing, access to the SRAM is disabled

1 Internal SRAM initialization is done, access to the SRAM is enabled

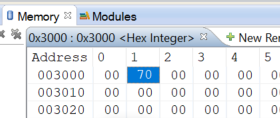

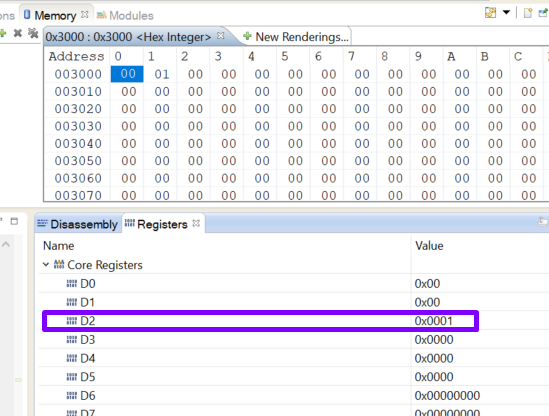

CW startup routine seems not waiting for RDY==1. But setting reset vector to iaprstvect() routine and power cycling board I see 0x0070 loop count @ 0x3000. :

void _Startup(void);

#pragma NO_RETURN

void iaprstvect(void)

{

__asm{

CLR D2

rdlp: INC D2

BRCLR.B ECCSTAT, #0, rdlp

ST D2, 0x3000 // save loop count

JMP _Startup

}

Looks like it takes quite a lot at power on to initialize ECC RAM. Long enough for default startup routine to set stack pointer and jump (BSR) to DoZeroOut() routine before ECC RAM initialization completes! Are there chances for big failure like reading wrong address from stack when returning back from DoZeroOut() to _Startup()?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Edward,

It doesn't matter whether you post it here or create a ticket.

But in this case, it doesn't seem to be a bug.

I tried the code you posted right in the _Startup function like this on S12ZVCA19 devkit

__EXTERN_C void _Startup(void) {

__asm{

CLR D2

rdlp: INC D2

BRCLR.B ECCSTAT, #0, rdlp

ST D2, 0x3000 // save loop count

}

__asm{

LD S, #__SEG_END_SSTACK-1 /* initialize SP */

#ifdef __ALIGN_STACK_OPT__

TFR S, D6 /* align SP to 4*/

AND D6, #-4

TFR D6, S

#endif

}

DoZeroOut();

DoCopyDown();

#ifdef __cplusplus

__static_init();

#endif

main();

} The counter showed 0x70.

But if the code is modified to write the SRAM while RDY == 0, the execution stalls at the ST instruction and the SRAM is written once the SRAM has become ready.

__EXTERN_C void _Startup(void) {

__asm{

CLR D2

rdlp: INC D2

ST D2, 0x3000 // save loop count

BRCLR.B ECCSTAT, #0, rdlp

}

__asm {

LD S, #__SEG_END_SSTACK-1 /* initialize SP */

#ifdef __ALIGN_STACK_OPT__

TFR S, D6 /* align SP to 4*/

AND D6, #-4

TFR D6, S

#endif

}

DoZeroOut();

DoCopyDown();

#ifdef __cplusplus

__static_init();

#endif

main();

}Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thank you! I tried enabling TIM0 and using TCNT to measure RDY delay time. Waiting for RDY=1 with leading write to RAM vs no leading write to RAM produces about the same reading in TCNT and different loop counter. Yes, it looks like a stall. Clearly S12ZVC RM is wrong and should be fixed. This is what we have:

7.3.4 Memory Initialization

To avoid spurious ECC error reporting, memory operations that allow a read before a first write (like the

read-modify-write operation of the unaligned access) require that the memory contains valid ECC values

before the first read-modify-write access is performed. The ECC module provides logic to initialize the

complete memory content with zero during the power up phase. During the initialization process the access

to the SRAM is disabled and the RDY status bit is cleared. If the initialization process is done, SRAM

access is possible and the RDY status bit is set.

Access disabled(ignored) vs stalled are not the same things. Bold part sounds as if initialization may never complete.

Regards,

Edward

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Edward,

I agree, it will be reported.

Thank you,

BR, Daniel