- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- Re: p2040 booting from spi flash

p2040 booting from spi flash

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

p2040 booting from spi flash

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am starting a new design and want to use a SPI flash for the RCW, PBI and to hold a u-boot image. I have set up the cfg_rcw_src[0:4] hardware pins and now I am filling in the 512 bits of the RCW. The PBI_SRC is set to 0101b for SPI 24-bit addressing but I am confused about the BOOT_LOC field as there does not appear to be a SPI option. I would like to know what I should use for these 4 bits so that it boots properly.

I have examined the start_here.html document in SDK v1.2.3 which seems to outline what I would like to do but details are sparse on how to generate the PBL image to do what I want.

Any help on this is much appreciated. Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please find below the full procedure that I used some time ago using cmd tools and FlashProgrammer from CodeWarrior. You need to use CodeWarrior + Processor Expert tool for generating the final PBL image. You can find here (http://cache.freescale.com/files/soft_dev_tools/doc/user_guide/QORIQCSPBLUG.pdf ) a full documentation about how you can make the project and all the necessary settings -- please read it FIRST.

The Corenet Soc is capable of booting from eSPI/SD/NAND. The bootup process can be divided into two stages: the first stage will load RCW and write configuration registers to initialize SPI interface, and configure one CPC as 1M SRAM, and loads U-boot image to the CPC. The second stage will configure all the hardware and boot up to U-Boot command line.

The PBL image contains three parts, the first is RCW, the second is PBI commands performs configuration registers write, the third is the 512KB u-boot image.

- Producing RCW

After creating a QorIQ Configuration Project, the project appears in the Project Panel view. Find "PBL Data" In window "Component Inspector", select "Input Format" value to be "RCW[0:511] U-Boot CCSR Dump", click button in the "Value" column of row "Input Data", a "String list editor" window pop up, paste RCW of u-boot dump into it, replace "fe8" in the second row with "580" (for p3060 please use "980" instead) and click "OK". Make sure the "Offset" is "0", the "Output Format" is "XXD Object Dump".

- Producing ACS File

Took an example for P3041: (please note that for P2040RDB you need to use P2041RDB - P2040 is not present in the boards.cfg file, but mostly is the same processor as P2041)

- For eSPI boot

- make P3041DS_SPIFLASH

- For SD boot

- make P3041DS_SDCARD

- For NAND boot

- make P3041DS_NAND

Using following command to convert the "u-boot.bin" to a xxd object dump file:

xxd u-boot.bin > u-boot.xxd

- Producing PBI commands

Click button in "Value" column of row "PBI Data input", a "PBI Data input" view will appears, paste commands below into text field, select "ACS File (XXD Object Dump)", change Offset to "f80000" and click "Browse" to select the file "u-boot.xxd" produced above, and click "Add", content of the "u-boot.xxd" will be pasted after the commands, then paste "09138000 00000000" and "091380c0 00000000" at the end. Click "Apply".

PBI Data

09010000 00200400

09138000 00000000

091380c0 00000100

09010100 00000000

09010104 fff0000b

09010f00 08000000

09010000 80000000

09000d00 00000000

09000d04 fff00000

09000d08 81000013

09000010 00000000

09000014 ff000000

09000018 81000000

09110000 80000403

09110020 2d170008

09110024 00100008

09110028 00100008

0911002c 00100008

09138000 00000000

091380c0 00000000

- Producing PBL image

- Find and click "Generate Processor Expert Code" in menu "Project", after it finished, click "Generated_Code" in "Project Panel" window and "PBL1.pbl" appears, find the file "PBL1.pbl" in workspace of this project.

- xxd -r PBL1.pbl > u-boot.pbl

- Put image to eSPI/SD/NAND and boot from there

Write u-boot.pbl and ucode(ucode.bin for example) to eSPI/SD/NAND in u-boot.

- For eSPI boot - for steps a & b you can simply use FlashProgrammer from CodeWarrior

- write u-boot.pbl to eSPI from offset 0x0

- tftp 100000 u-boot.pbl

- sf probe 0

- sf erase 0 100000

- sf write 100000 0 $filesize

- write ucode to eSPI from offset 0x110000

- tftp 100000 ucode.bin

- sf erase 110000 10000

- sf write 100000 110000 $filesize

- change dip-switch

- for P3041/P4080/P5020: Change SW1[1:5] = off off on on off, then power on.

- for P2041: Change SW1[1:5] = off on on off off, then power on.

- write u-boot.pbl to eSPI from offset 0x0

- For SD boot

- write u-boot.pbl to SD from offset block 8

- tftp 100000 u-boot.pbl

- mmcinfo

- mmc write 100000 8 441

- write ucode.bin to SD from block 1130 (0x46a)

- tftp 100000 ucode.bin

- mmc write 100000 46a 10

- change dip-switch

- for P3041/P4080/P5020: Change SW1[1:5] = off off on on off, then power on.

- for P2041: Change SW1[1:5] = off on on off off, then power on.

- write u-boot.pbl to SD from offset block 8

- For NAND boot - for steps a & b you can simply use FlashProgrammer from CodeWarrior

- write u-boot.pbl to NAND from offset 0x0

- tftp 100000 u-boot.pbl

- nand info

- nand erase 0 a0000

- nand write 100000 0 $filesize

- write ucode.bin to NAND from offset 0xc0000

- tftp 100000 ucode.bin

- nand erase c0000 20000

- nand write 100000 c0000 $filesize

- change dip-switch

- Change SW1[1:5] = off on off off on, Change SW7[1:4] = on off off on, then power on.

- write u-boot.pbl to NAND from offset 0x0

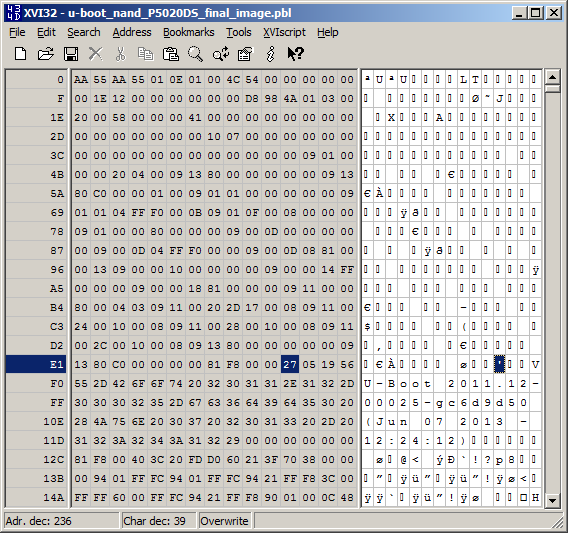

I added a final SPI PBL file for P3041DS for having an example about what you must obtain in the final.

Regards,

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

All the documentation talks about the PBL image consisting of three parts: RCW, PBI commands, and the u-boot image. I always interpreted this as meaning that the u-boot image was simply concatenated at the end of the PBL binary, and the loader would just magically know how many bytes to read from the SPI flash after the last PBI command and know where to store it in SRAM.

The reality is, the PBL image actually consists of just RCW and PBI commands. The u-boot image is broken up into 64-byte chunks and embedded in a series of PBI commands that tell the loader what memory address the 64-byte chunk is to be copied to.

Is this a correct interpretation of how the spi flash boot operation works?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As already described above, the bootup process from SPI can be divided into two stages:

- the first stage will load RCW and write configuration registers to initialize SPI interface, and configure CPC1 as 1M SRAM, and loads U-boot image to CPC1.

- the second stage will configure all the hardware and boot up to U-Boot command line.

The PBL image contains three parts, the first is RCW, the second is PBI commands performs configuration registers write, the third is the 512KB u-boot image.

Please find below the PBI data commands description:

+ PBI DATA | Description

+ -------------------------------------------------

+ | 09010000 00200400 | CPCFI & |

+ | 09138000 00000000 | CPCLFC |

+ | 091380c0 00000100 | |

+ -------------------------------------------------

+ | 09010100 00000000 | Configure |

+ | 09010104 fff0000b | CPC1 as |

+ | 09010f00 08000000 | 1M SRAM |

+ | 09010000 80000000 | |

+ -------------------------------------------------

+ | 09000d00 00000000 | Configure |

+ | 09000d04 fff00000 | LAW of |

+ | 09000d08 81000013 | CPC1 |

+ -------------------------------------------------

+ | 09000010 00000000 | Configure |

+ | 09000014 ff000000 | Alternate |

+ | 09000018 81000000 | |

+ --------------------------------------------------

+ | 09110000 80000403 | Initialize |

+ | 09110020 2d170008 | SPI interface|

+ | 09110024 00100008 | |

+ | 09110028 00100008 | |

+ | 0911002c 00100008 | |

+ -----------------------------------------------------

+ | 09138000 00000000 | Flush command |

+ | 091380c0 00000000 | |

+ -----------------------------------------

So regarding your assumptions is more appropriate to your first attempt, but is not something so "magical", is pretty simple to know where the u-boot starts, because it begins with <boot signature> - 27 05 19 56 55 2D 42 6F 6F 74

Regards,

Marius

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What procedure did you use to get the u-boot image to be in segments. I see 0x81F80000 (followed by 64 bytes) and then 0x81f80040 (followed by another 64 bytes). Is this done automatically with "make P3041DS_SPIFLASH" or is there another processing step that we must follow?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

make P3041DS_SPIFLASH will generate u-boot binary file. But, to have u-boot image necessary for SPI boot (rcw + pbi + u-boot), you should follow the steps described by Marius. We used Processor Expert Software: QorIQ Configuration Suite as a configuration tool.

More information about QorIQ Configuration Suite PBL Configuration Tools you can find at this link:

QorIQ Configuration Suite PBL Configuration Tool

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Marius,

thanks for your responses and U-Boot image!

Can you please also explain meaning of last 4 bytes in the PBL : hex value 81 F8 00 00 (after 091380c0 00000000 wait command and before U-Boot signature 27 05 19 56).

When I import the PBL image (taken from U-Boot image) in QCS project and generate new binary RCW+PBL image QCS adds checksum value in the end (instead of 81 81 F8 00 00 value QCS adds checksum e.g. 08 13 80 40 8B 97 14 AF). The problem is that this new generated RCW seems not to transfer control to U-Boot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please ignore my previous question. I've just missed the part with XXD obj dump and used binary image (as with P10xx OnChipRom). Now PBL seems to work as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the quick responses. I really like the features of this chip.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For the PBL image producing, please refer to START_HERE.html->Boot up from eSPI/SD/NAND on corenet ds boards (Linux BSP)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For your case, BOOT_LOC should be set to "Memory Complex 1"