- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How do I make the S32R45 support nvme?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I use "fsl-auto-rsdk-bsp-v33.0.tar.gz" to build fsl-image-auto.

How should I modify the device tree to support nvme?

Is there a reference document?

It' my device tree

serdes0: serdes@40480000 {

#phy-cells = <3>;

compatible = "nxp,s32cc-serdes";

clocks = <&clks S32GEN1_SCMI_CLK_SERDES_AXI>,

<&clks S32GEN1_SCMI_CLK_SERDES_AUX>,

<&clks S32GEN1_SCMI_CLK_SERDES_APB>,

<&clks S32GEN1_SCMI_CLK_SERDES_REF>;

clock-names = "axi", "aux", "apb", "ref";

resets = <&reset S32GEN1_SCMI_RST_SERDES0>,

<&reset S32GEN1_SCMI_RST_PCIE0>;

reset-names = "serdes", "pcie";

fsl,sys-mode = <PCIE_GEN3X2_MODE>;

reg = <0x0 0x40480000 0x0 0x108>,

<0x0 0x40483008 0x0 0x10>,

<0x0 0x40482000 0x0 0x800>,

<0x0 0x40482800 0x0 0x800>;

reg-names = "ss_pcie", "pcie_phy", "xpcs0", "xpcs1";

status = "okay";

};

but.

[ 1.548300] phy-s32gen1-serdes 40480000.serdes: Using mode 0 for SerDes subsystem

[ 1.548970] phy-s32gen1-serdes 44180000.serdes: Using mode 0 for SerDes subsystem

[ 1.549965] phy_mode = 0 40400000.pcie: Configured as RootComplex

[ 1.549970] sctrl->ext_clk=1

[ 1.549973] start!

[ 1.554963] end!

[ 1.554971] phy-s32gen1-serdes 40480000.serdes: Failed to lock PCIE phy

[ 1.554980] phy phy-40480000.serdes.0: phy poweron failed --> -110

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

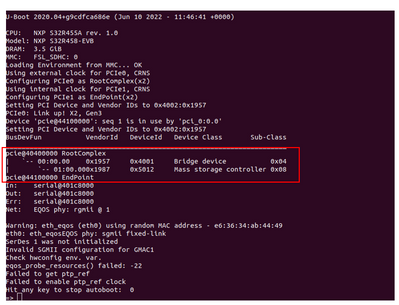

The BSP 33 should support the NVMe via PCIe by default. When booting, U-Boot should detect the device. Please refer to the attached image. In Linux, the device is detected under /dev/nvme0 and /dev/nvme0n1. You can create a partition in /dev/nvme0n1 with fdisk and format it via mkfs.ext3.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

It seems to me a clock problem. Can you try the below command in Uboot? and check the clock frequencies? On my side I get the next output:

=> verifclk CMU | Monitored | Reference | Expected | Verified

ID CLOCK CLOCK RANGE (MHZ) RANGE (MHZ)

| 0 | FXOSC | FIRC | 40.000 | 39.062 |

| 1 | FIRC | FXOSC | 48.000 | 48.146 |

| 2 | SIRC | FXOSC | 0.032 | 0.031 |

| 3 | FTM_0_REF | FXOSC | 40.000 | 39.976 |

| 4 | FTM_1_REF | FXOSC | 40.000 | 39.976 |

| 5 | XBAR_DIV3 | FIRC | 133.333 | 125.000 |

| 6 | XBAR_M7_0 | FIRC | 400.000 | 375.000 |

| 7 | XBAR_DIV3 | FXOSC | 133.333 | 132.812 |

| 8 | XBAR_M7_1 | FIRC | 400.000 | 375.000 |

| 9 | XBAR_M7_2 | FIRC | 400.000 | 375.000 |

| 10 | PER | FIRC | 80.000 | 78.125 |

| 11 | SERDES_REF | FXOSC | 100.000 - 125.000 | 99.609 |

| 12 | FLEXRAY_PE | FXOSC | 40.000 | 0.000 - 0.015 |

| 13 | CAN_PE | FXOSC | 80.000 | 80.078 |

| 14 | GMAC_0_TX | FXOSC | 125.000 | 125.000 |

| 15 | GMAC_TS | FXOSC | 200.000 | 0.000 - 0.015 |

| 16 | LIN | FXOSC | 125.000 | 62.500 |

| 17 | QSPI_1X | FXOSC | 133.333 | 132.812 |

| 18 | SDHC | FXOSC | 400.000 | 398.437 |

| 20 | DDR | FIRC | 800.000 | 750.000 |

| 21 | GMAC_0_RX | FXOSC | 2.500 - 125.000 | 24.902 |

| 22 | SPI | FXOSC | 100.000 | 99.609 |

| 27 | A53_CORE | FXOSC | 800.000 | 796.875 |

| 28 | A53_CORE | FIRC | 800.000 | 750.000 |

| 38 | ACCEL3 | FXOSC | 600.000 | 601.562 |

| 39 | ACCEL4_0 | FXOSC | 400.000 | 398.437 |

| 40 | ACCEL4_0 | FXOSC | 400.000 | 398.437 |

| 46 | GMAC_1_TX | FXOSC | 125.000 | 0.000 - 0.015 |

| 51 | GMAC_1_RX | FXOSC | 125.000 | 47.851 |

| 52 | MIPICSI2_0 | FXOSC | 400.000 | 398.437 |

| 53 | MIPICSI2_0 | FXOSC | 400.000 | 398.437 |

| 54 | SERDES_REF | FXOSC | 125.000 | 99.609 |

After this, you can try to use the internal clock instead: The customer has to modify the next environment variable in Uboot:

=> print hwconfig

hwconfig=pcie0:mode=rc,clock=ext;pcie1:mode=ep,clock=int

=> edit hwconfig

edit: pcie0:mode=rc,clock=int;pcie1:mode=ep,clock=int

=> saveenv

Saving Environment to MMC... Writing to MMC(0)... OK

Then reset the board and see if the MPLLs is still unlocked.

Please share the results.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Our board hardware has a power supply problem,Now it can detect nvme。

in addition,we find write speed is too slow in cache mode(170MB/s)。Direct mode seems to be normal(852MB/s).

root@s32r45evb:/mnt/nvme# dd if=/dev/zero of=test bs=8M count=256

256+0 records in

256+0 records out

2147483648 bytes (2.1 GB, 2.0 GiB) copied, 12.5997 s, 170 MB/s

root@s32r45evb:/mnt/nvme# dd if=/dev/zero of=test bs=8M count=256 oflag=direct

256+0 records in

256+0 records out

2147483648 bytes (2.1 GB, 2.0 GiB) copied, 2.52067 s, 852 MB/s

We wrote a test program,The average write speed is around 250MB/s,.here's still a gap in the write speed that we want.

Why is cache mode lower than direct mode?

Can it be optimized?

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I heard from Horace Hou, this issue has been discussed through emails last week. So I suggest we can close this case now. Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I have contact our RADAR team and ask for help.

I will feedback you ASAP.

Best regards,

Peter