- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 基于模型的设计工具箱(MBDT)

- :

- 基于模型的设计工具箱(MBDT)

- :

- Re: Using NVM chip on MPC5775B EVB

Using NVM chip on MPC5775B EVB

Using NVM chip on MPC5775B EVB

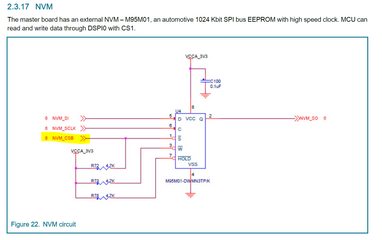

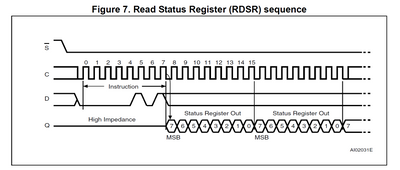

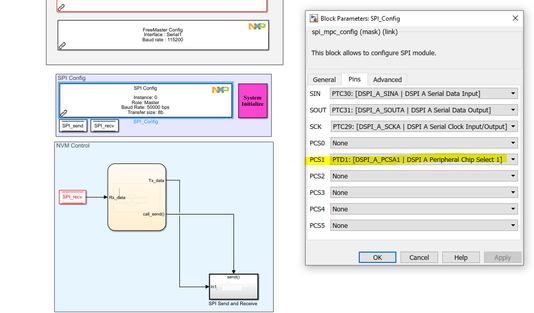

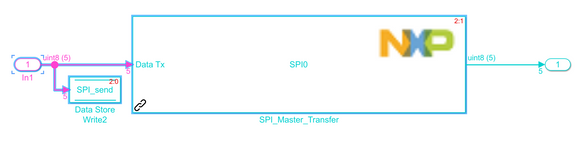

I would like to use NVM chip (M95M01-DWMN3TP/K) on DVCU5775EVM, so initially I have prepared simple model just to check chip status.

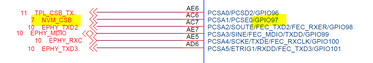

Chip is connected to SPI0 with CS1

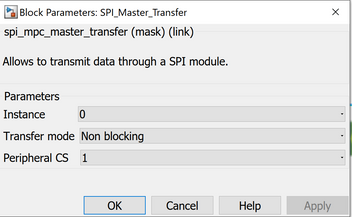

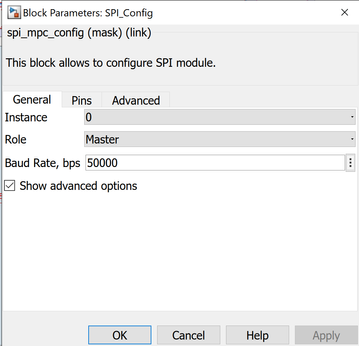

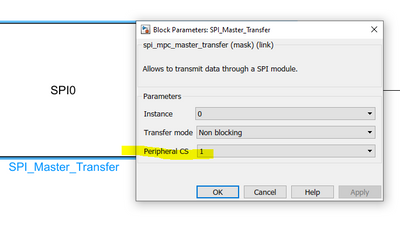

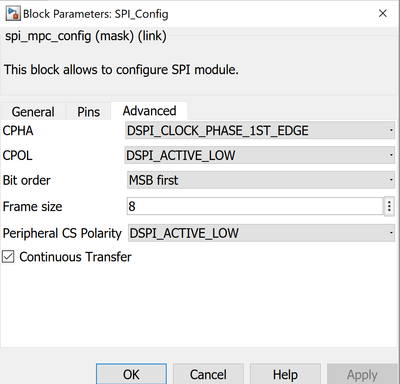

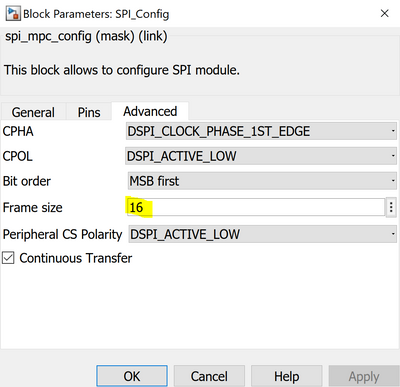

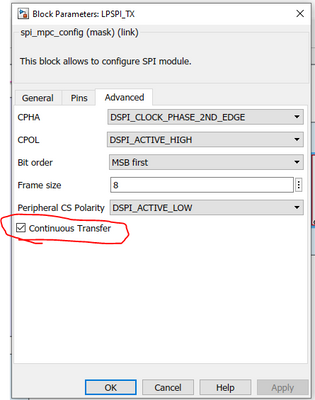

And I have used these settings for SPI blocks

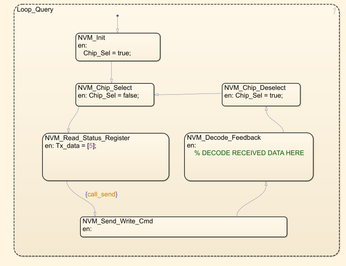

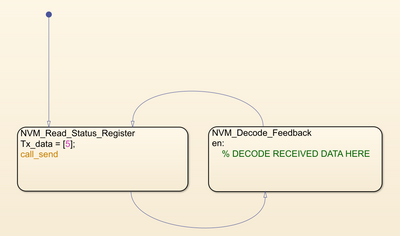

Then have prepared stateflow diagram to send control commands

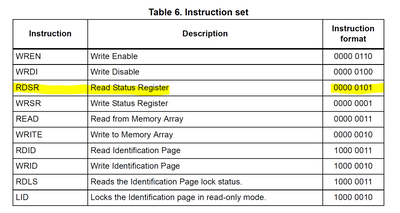

where Tx_data is control command (RDSR) from M95M01 datasheet

and this command goes after chip is selected

Finally I have got following model.

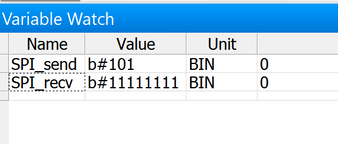

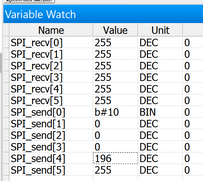

After flashing, I have used Freemaster to check SPI feedback signal from NVM and it is always 0xff.

Hello @sonik82 ,

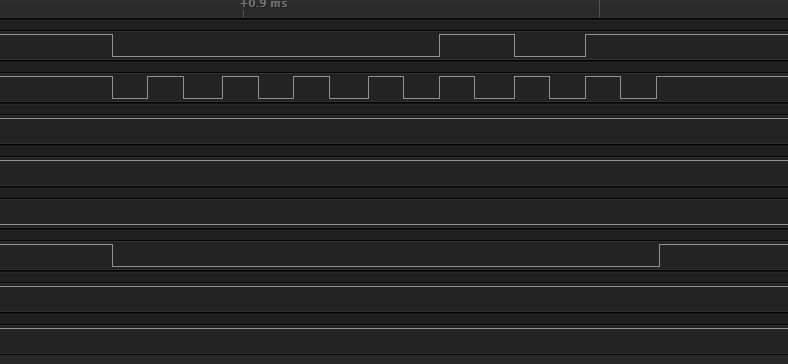

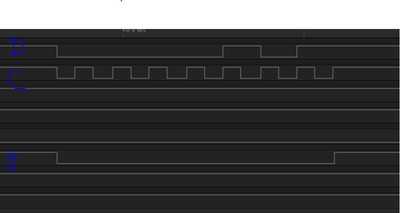

I had a look at your model and attached the model with a couple of changes. I don't have access to your board and I cannot test it, but I had a look at the signals using the logic analyzer. See the image attached below.

1. SPI settings - for that you can select the CS pin in the SPI_Config, you don't need to change it by hand. To select the device you can select the CS in the Master transmit block, the one you have already used.

2. In the Stateflow, you can remove the chip select state, because the DSPI will handle that, so you can only send and decode the responses from the SPI.

Hope this helps,

Marius

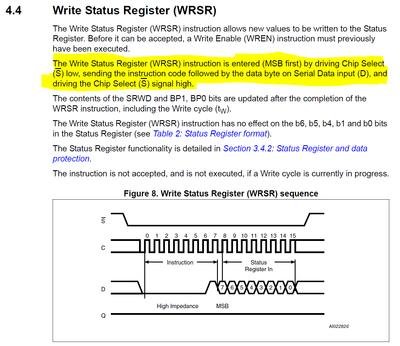

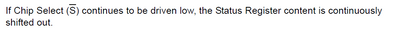

As per datasheet, we need to keep Chip select low while sending command and getting data from chip

Your image shows that Chip Select goes High after transmitting of command, am I right?

Is it possible to keep this signal Low until we will get data?

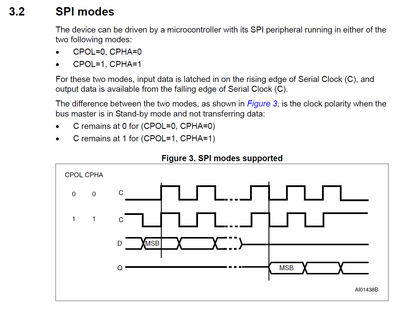

Another question, these SPI settings are correct

to provide one of following SPI modes?

Also, to send 8 bits command and 24 bits address I need to change SPI frame size to 32, am I right? Then how to change this frame size dynamically? For example to Read Status Register it is required only 8 bits, to Read data 8 bits for command + 24 bits for address, to Write data 8 bits for command + 24 bits for address + Data.

Input and Output ports have same size, so does it mean that we can only send/get SPI frames with same size?

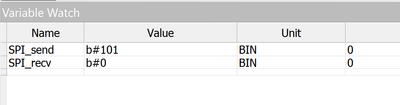

I have changed SPI frame size from 8 to 16 bits, assuming that Chip select will be Low enough time to read feedback (8 bits) from NVM chip.

Now my SPI receive data is 0.

It looks fine for Read Status Register command, because bits 0,1,2,3,7 should not be set by default.

I am going to check Read/Write commands.

Hello @sonik82 ,

You can send variable bytes number (8, 16, 24, 32, 40 ...) with a continuous CS by selecting the Continuous transfer. But I've seen that you have already done that.

So, you select the frame size as 8, and you populate an array with the commands you want to send. F4irst byte is the command, then the next 3 bytes are the address. If you provide such an array to the SPI Send block, this will output on bus 4 continuous bytes, with only one chip select transition.

Hope this helps,

Marius

Hello @sonik82 ,

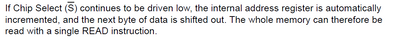

I think it will remain low as long as you transmit. But, if you expect to receive for example 4 bytes from the NVM chip, you can compute the array like this: [cmd, addr, addr, add, 0xFF, 0xFF, 0xFF, 0xFF] basically you send an 0xFF or 0x00 as long as you want to receive from the NVM chip. Please give this a try.

Marius

Hello @mariuslucianand

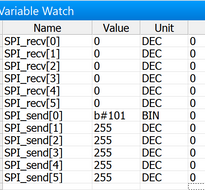

I have checked your idea. To do it, I have modified model by creation of 4 commands:

RDSR (Read Status Register) [ 00000101 0xFF 0xFF 0xFF 0xFF 0xFF 0xFF]

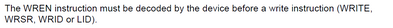

WREN (Write Enable) [ 00000110 0xFF 0xFF 0xFF 0xFF 0xFF 0xFF] because of

WRITE (Write to Memory Array) [ 00000010 0x00 0x00 0x00 11000100 0xFF]

READ (Read from Memory Array) [ 00000011 0x00 0x00 0x00 0xFF 0xFF]

When I use SPI frame size, received data is always 0xFF.

Same situation with SPI frame size 16, but with using size 24 output data becomes 0x00