- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

MCF54415 USB Clock setting

Hi,

I am using MCF54415 custom built board with MQX and intend to use USB OTG on it.

However, I am facing USB clock setting issue. The problem is I cannot change OUTDIV4 bits in PLL Divider Register (PLL_DR).

I can see during dubug, in register PLL_DR the value is 0x00030460. But when I change it to 0x00070406, it remains the same even after execution of the PLL_DR = 0x00070406 command.

Any hints or suggestions are greatly appreciated.

Thank you for your time.

-Nitin

Hi Nitin,

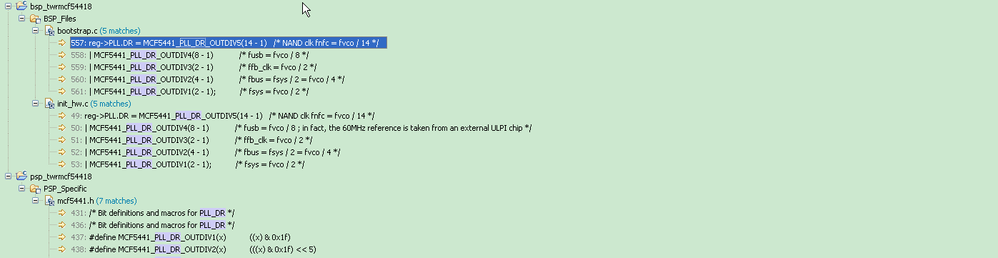

I am not sure which version of MQX that you are using, from the current MQX 4.1, I just found the BSP for MCF54418, and only two places modify that register, so I am suspecting if you just modified one place and the other still kept the old settings. Please kindly refer to the following for details.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Kan,

Thank you for the response.

We are using MQX 4.0.1 and we have the same settings as in the snap posted by you.

However, on reading the value of PLL_DR, we get OUTDIV4 = 3.

No matter at how many places we change the value of OUTDIV4, we always get 3.

Even in BSP, the value of OUTDIV4 is set to 7, but during debugging it shows 3.

Do I need to change anything else to change this value ?

Please let me know if you need more information over it.

Thanks for your time.

Nitin

Hi Nitin,

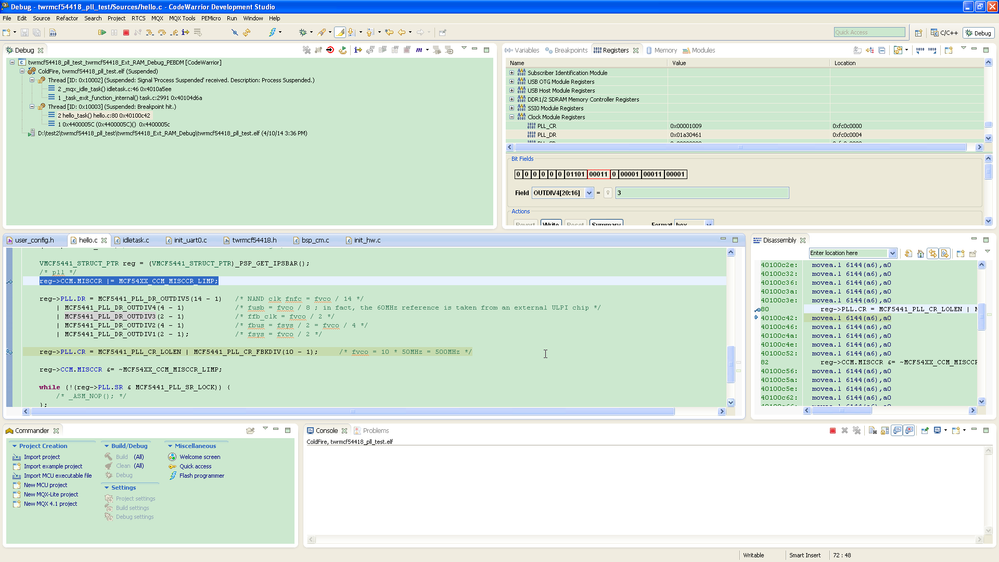

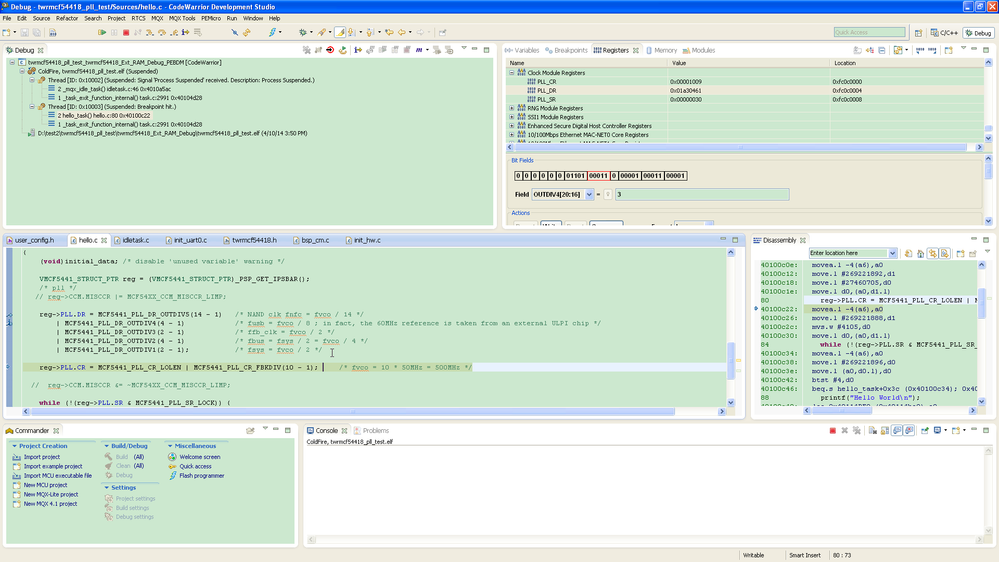

As I just have TWR-MCF54418 on hand , so I just did simple test based that board, actually I found PLL_DR can be modified as any value as you mentioned, you know , RM says "The PLL_DR[OUTDIVn] fields can be changed during normal operation or when the device is in limp mode." so I tried that in both modes, DIV4 can be changed to 3 in any test, but I am not sure how you change PLL_DR, but I'd like to recommend changing PLL_DR under limp mode. Would you please help to clarify? Please kindly refer to the following for details.

Limp mode test:

Normal mode test:

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------