- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SPI 0&SPI 2

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I want to use SPI0 and SPI2 are set to the MASTER mode to configure two chips.My SPIO configuration no problem, but SPI2 can not read the data. I can see the data sent and returned on my oscilloscope. But the data out of the register can not be written into。MCU is 5775K .

IO: //SPIO CLK

SIUL2.MSCR[SPI0_SCK_MSCR_NB].R = MSCR_OUTPUT|SPI0_SCK_MSCR_SSS;

SIUL2.MSCR[SPI0_SCK_MSCR_NB].B.SRC = 3; /* Full strength slew rate */

//SPIO SOUT

SIUL2.MSCR[SPI0_SOUT_MSCR_NB].R = MSCR_OUTPUT|SPI0_SOUT_MSCR_SSS;

SIUL2.MSCR[SPI0_SOUT_MSCR_NB].B.SRC = 3; /* Full strength slew rate */

//SPIO SIN

SIUL2.MSCR[SPI0_SIN_MSCR_NB].R = MSCR_INPUT;

//SPIO CS

SIUL2.MSCR[SPI0_CS0_MSCR_NB].R = MSCR_OUTPUT|SPI0_CS0_MSCR_SSS;

SIUL2.MSCR[SPI0_CS0_MSCR_NB].B.SRC = 3; /* Full strength slew rate */

//SPI2 CLK

SIUL2.MSCR[SPI2_SCK_MSCR_NB].R = MSCR_OUTPUT|SPI2_SCK_MSCR_SSS;//10

SIUL2.MSCR[SPI2_SCK_MSCR_NB].B.SRC = 3;

//SPI2 SOUT

SIUL2.MSCR[SPI2_SOUT_MSCR_NB].R = MSCR_OUTPUT|SPI2_SOUT_MSCR_SSS;//12

SIUL2.MSCR[SPI2_SOUT_MSCR_NB].B.SRC = 3;

//SPI2 SIN

SIUL2.MSCR[SPI2_SIN_MSCR_NB].R = MSCR_INPUT;//13

//SPI2 CS

SIUL2.MSCR[SPI2_CS0_MSCR_NB].R = MSCR_OUTPUT|SPI2_CS0_MSCR_SSS;//10

SIUL2.MSCR[SPI2_CS0_MSCR_NB].B.SRC = 3;

void SPI0_Init(void)

{

SPI_0.MCR.R = 0x80010001; /* Configure SPI as master */

SPI_0.MODE.CTAR[0].B.DBR = 0; /* 50/50 duty cycle */

SPI_0.MODE.CTAR[0].B.FMSZ = 15; /* 16 bits per frame */

SPI_0.MODE.CTAR[0].B.CPOL = 0; /* Inactive state value of SCK is low */

SPI_0.MODE.CTAR[0].B.CPHA = 0; /* Data captured and then changed */

SPI_0.MODE.CTAR[0].B.LSBFE = 0; /* MSB first */

/* Tcsc = 1/fp * PCSSCK * CSSCK */

SPI_0.MODE.CTAR[0].B.PCSSCK = 3; /* 7, PCS to SCK delay prescaler */

SPI_0.MODE.CTAR[0].B.CSSCK = 0; /* 2, PCS to SCK delay scaler */

/* Tasc = 1/fp * PASC * ASC */

SPI_0.MODE.CTAR[0].B.PASC = 0; /* 1, After SCK delay prescaler */

SPI_0.MODE.CTAR[0].B.ASC = 0; /* 2, After SCL delay scaler */

/* Tdt = 1/fp * PDT * DT */

SPI_0.MODE.CTAR[0].B.PDT = 3; /* 7, Delay after transfer prescaler */

SPI_0.MODE.CTAR[0].B.DT = 0; /* 2, Delay after transfer scaler */

/* baud rate = fp/PBR * (1+DBR)/BR */

SPI_0.MODE.CTAR[0].B.PBR = 3; /* 7, Baud rate prescaler */

SPI_0.MODE.CTAR[0].B.BR = 0; /* 2, Baud rate scaler */

SPI_0.MCR.B.HALT = 0x0; /* Exit HALT mode: go from STOPPED to RUNNING state*/

}

void SPI2_Init(void)

{

SPI_2.MCR.R = 0x80010001; /* Configure SPI as master */

SPI_2.MODE.CTAR[0].B.DBR = 0; /* 50/50 duty cycle */

SPI_2.MODE.CTAR[0].B.FMSZ = 15; /* 16 bits per frame */

SPI_2.MODE.CTAR[0].B.CPOL = 0; /* Inactive state value of SCK is low */

SPI_2.MODE.CTAR[0].B.CPHA = 0; /* Data captured and then changed */

SPI_2.MODE.CTAR[0].B.LSBFE = 0; /* MSB first */

/* Tcsc = 1/fp * PCSSCK * CSSCK */

SPI_2.MODE.CTAR[0].B.PCSSCK = 3; /* 7, PCS to SCK delay prescaler */

SPI_2.MODE.CTAR[0].B.CSSCK = 0; /* 2, PCS to SCK delay scaler */

/* Tasc = 1/fp * PASC * ASC */

SPI_2.MODE.CTAR[0].B.PASC = 0; /* 1, After SCK delay prescaler */

SPI_2.MODE.CTAR[0].B.ASC = 0; /* 2, After SCL delay scaler */

/* Tdt = 1/fp * PDT * DT */

SPI_2.MODE.CTAR[0].B.PDT = 3; /* 7, Delay after transfer prescaler */

SPI_2.MODE.CTAR[0].B.DT = 0; /* 2, Delay after transfer scaler */

/* baud rate = fp/PBR * (1+DBR)/BR */

SPI_2.MODE.CTAR[0].B.PBR = 3; /* 7, Baud rate prescaler */

SPI_2.MODE.CTAR[0].B.BR = 0; /* 2, Baud rate scaler */

SPI_2.MCR.B.HALT = 0x0; /* Exit HALT mode: go from STOPPED to RUNNING state*/

}

void SPI0_Transmit(SPI_CS csn, uint16_t sout, uint16_t *sin)

{

SPI_0.PUSHR.PUSHR.R = 0x08000000 | (uint32_t)csn << 16 | (uint32_t)sout;

while (SPI_0.SR.B.TCF == 0);

SPI_0.SR.B.TCF = 1;

*sin = SPI_0.POPR.R;

}

void SPI2_Transmit(SPI_CS csn, uint16_t sout, uint16_t *sin)

{

SPI_2.PUSHR.PUSHR.R = 0x08000000 | (uint32_t)csn << 16 | (uint32_t)sout;

while (SPI_2.SR.B.TCF == 0);

SPI_2.SR.B.TCF = 1;

*sin = SPI_2.POPR.R; //The problem is here

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

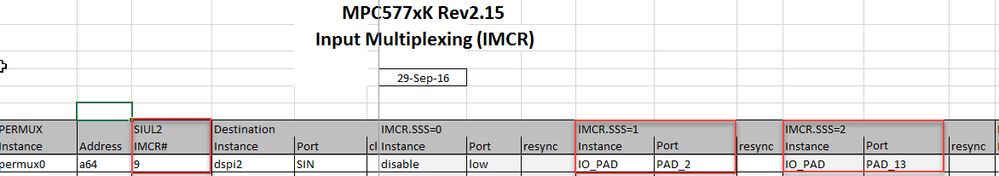

For the SPI2 SIN you also need to configure the IMCR register depending on used pad.

For pad PA2

SIUL2.IMCR[9].B.SSS = 1; /* SPI2 SIN: connected to pad2 */

For pad PA13

SIUL2.IMCR[9].B.SSS = 2; /* SPI2 SIN: connected to pad13 */

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

//SPI2 CLK

SIUL2.MSCR[SPI2_SCK_MSCR_NB].R = MSCR_OUTPUT|SPI2_SCK_MSCR_SSS;//11

SIUL2.MSCR[SPI2_SCK_MSCR_NB].B.SRC = 3;

//SPI2 SOUT

SIUL2.MSCR[SPI2_SOUT_MSCR_NB].R = MSCR_OUTPUT|SPI2_SOUT_MSCR_SSS;//12

SIUL2.MSCR[SPI2_SOUT_MSCR_NB].B.SRC = 3;

//SPI2 SIN

SIUL2.MSCR[SPI2_SIN_MSCR_NB].R = MSCR_INPUT;//13

//SPI2 CS

SIUL2.MSCR[SPI2_CS0_MSCR_NB].R = MSCR_OUTPUT|SPI2_CS0_MSCR_SSS;//10

SIUL2.MSCR[SPI2_CS0_MSCR_NB].B.SRC = 3;