- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Proper mpc5777m memory address connection

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

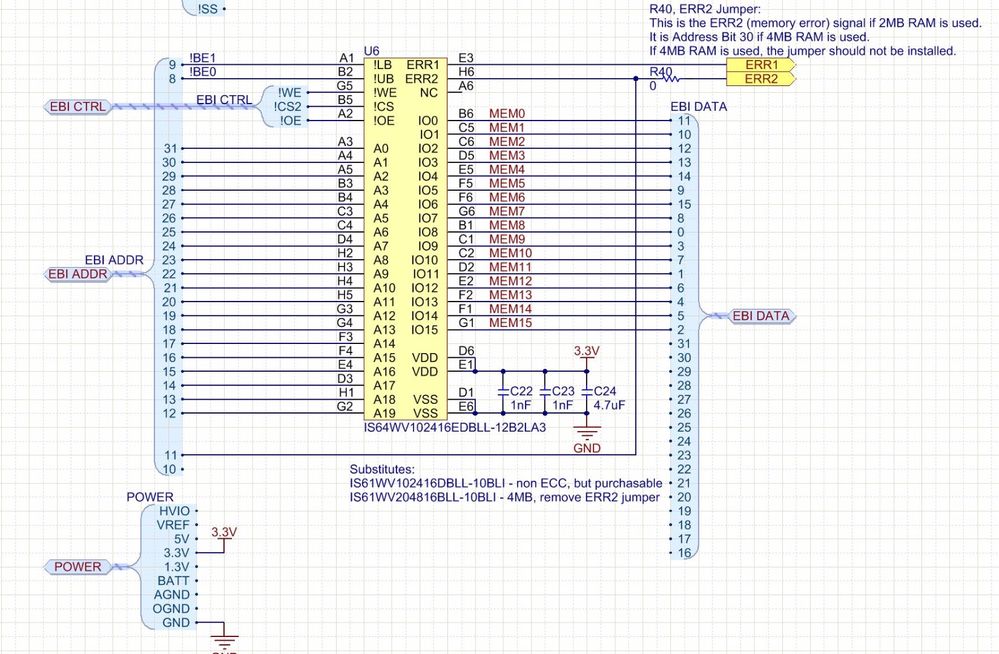

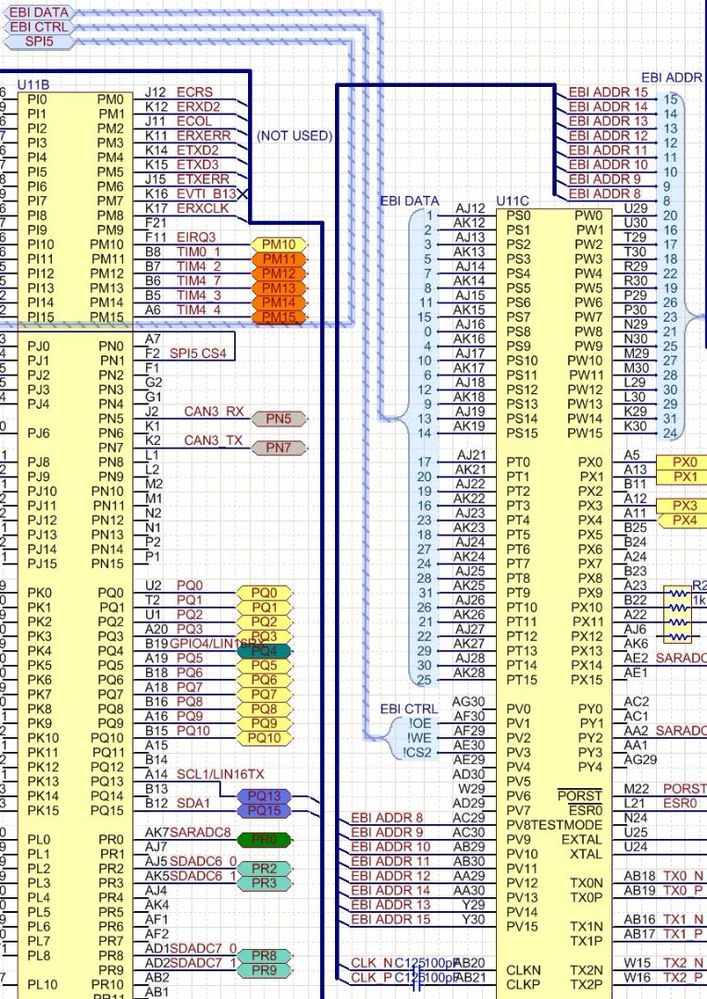

Electrical Engineer connecting mpc5777m EBI to a RAM chip. I am curious if I have connected the memory address lines correctly.

The mpc5777m EBI is connected to an SRAM BGA with 1024x 16 bit words and 19 address pins. I added a 20th address pin in case I use the 2048x 16 bit word version of that chip.

PowerPC is opposite endian, so I think that means address bit 31 from the processor is connected to address 0 of the RAM. PPC Address bit 12 is RAM bit 19. PPC bit 11 would be RAM address bit 20.

Then there are Byte enables. PPC 'address bit' 9 would be lower byte enable. PPC addr bit 8 would be upper byte enable.

Is my logic correct? Here are images of my wiring:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If APS=1, then can external address line A31 be connected to A0 pin of external flash or SRAM(16bit data bus)? Is the connection right?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, please take a look at following document, especially section 3, 4, 6:

https://community.nxp.com/docs/DOC-101725

I believe it answers your question.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

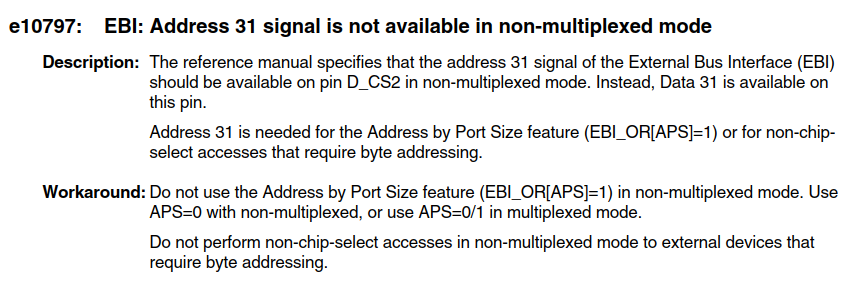

Does the "address by port size" bit (EBI_OR[APS]) allow the address lines for a 16 bit data port memory to start at 31 instead of 30?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Theoretically yes, but I know an erratum exists for MPC5777C device:

If you are in design stage I would rather recommend to connect it usual way.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We decided to try it, looks like APS=1 is working for us on the MPC5777M, so we are able to use the address line that would otherwise be unusable due to byte select muxing.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If APS=1, then can external address line A31 be connected to A0 pin of external flash or SRAM(16bit data bus)? Is the connection right? what is the result of your trying?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Is there a way to know if this errata also affects the MPC5777M? Does this errata also affect the 77M?