- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

I use MPC5745R as the main microcontroller.

A 20MHz oscillator is used and 150MHz CPU frequency is then set.

The following code runs correctly.

/************************************************************************************/

/************************************************************************************/

MC_CGM.AC3_SC.B.SELCTL=1; /*PLL0 uses an external oscillator*/

MC_CGM.AC4_SC.B.SELCTL=3; /*PLL1 source is PLL0 PHI1*/

/*20MHz XOSC->160MHz PLL0 PHI*/

/*

PLL0 PHI=Ref/(PREDIV*RFDPHI)*MFD

*/

PLLDIG.PLL0DV.B.RFDPHI = 2;

PLLDIG.PLL0DV.B.PREDIV = 1;

PLLDIG.PLL0DV.B.MFD = 16; /*8->127*/

/*

VCO_PLL0=Ref_PLL0*MFD*2/PREDIV

VCO_PLL0=20MHz*16*2/1=640MHz

*/

/*20MHz XOSC->40MHz PLL0 PHI1*/

/*

PLL0 PHI1=Ref/(PREDIV*RFDPHI1)*MFD

*/

PLLDIG.PLL0DV.B.RFDPHI1 = 8; /*4->15*/

/*40MHz PLL0 PHI1->150MHz PLL1 PHI*/

/*

PLL1 PHI=Ref*MFD/(RFDPHI*2)

*/

/*

VCO_PLL1=Ref_PLL1*MFD

VCO_PLL0=40MHz*30=1200MHz

*/

PLLDIG.PLL1DV.B.RFDPHI = 4;

PLLDIG.PLL1DV.B.MFD = 30;

/*System Clock Selector*/

MC_CGM.SC_DC[0].R = 0x80000000; /*FXBAR=150MHz*/

MC_CGM.SC_DC[1].R = 0x80010000; /*SXBAR=75MHz*/

MC_CGM.SC_DC[2].R = 0x80030000; /*PBRIDGE=37.5MHz*/

/************************************************************************************/

/************************************************************************************/

But if I change the PBRIDGE clock to 50MHz as following:

MC_CGM.SC_DC[2].R = 0x80020000; /*PBRIDGE=50MHz*/

Then my code runs wrong!!!

I don't why!

THe PBRIDGE clock must be half of the slow bar???

Thank you.

已解决! 转到解答。

Hi,

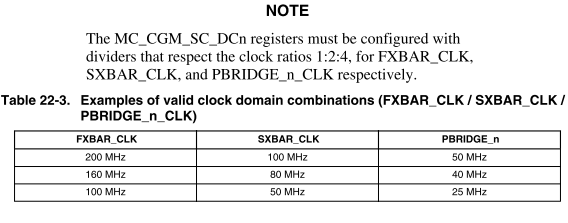

please look at the following table from reference manual.

This table shows, that PBRIDGE frequency has to be one quarter of system frequency (FXBAR_CLK).

Regards,

Martin