- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Mpc5746c communication problem in SDK UP9 as Slave

Mpc5746c communication problem in SDK UP9 as Slave

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Mpc5746c communication problem in SDK UP9 as Slave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NXP Support Team:

We had problem developing SPI for MPC5746C.

We hope that 5746C as Slave can communicate with I.MX8 through SPI.

But now I.MX8 can normally send and receive data, but 5746C has problems in both receiving and sending data.

MPC5746C development environment:

IED:S32DS

SDK:S32DS_PA_v2017.R1_UP9 (PS:S32DS_PA_v2017.R1_UP10 met same problem)

Channel:SPI_0:

Clock:PG[13]

SIN/MOSI: PG[10]

SOUT/MISO: PG[12]

SS: PG[11]

Problem:

We want 5746C to transfer 10 bytes of data{0x0D,0x05,0x01,0x00,0x05,0x05.....},But only 4 bytes were seen on the oscilloscope{0x00,0x0D,0x05,0x01,0x00,0x00,0x00,0x00.....}.

The I.MX8 has sent 15 bytes, but the MPC5746C cannot receive them.

In the picture above, the yellow line is CLOCK, the green line is MPC5746C SOUT.

I can't send all the original project, so I put the code related to SPI in the attachment.

In the attached project, the data that 5746C wants to transfer are {55,44,33,22,11,00,99,88,77,66},but all the datas display in oscilloscope is 0x16.

Best Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

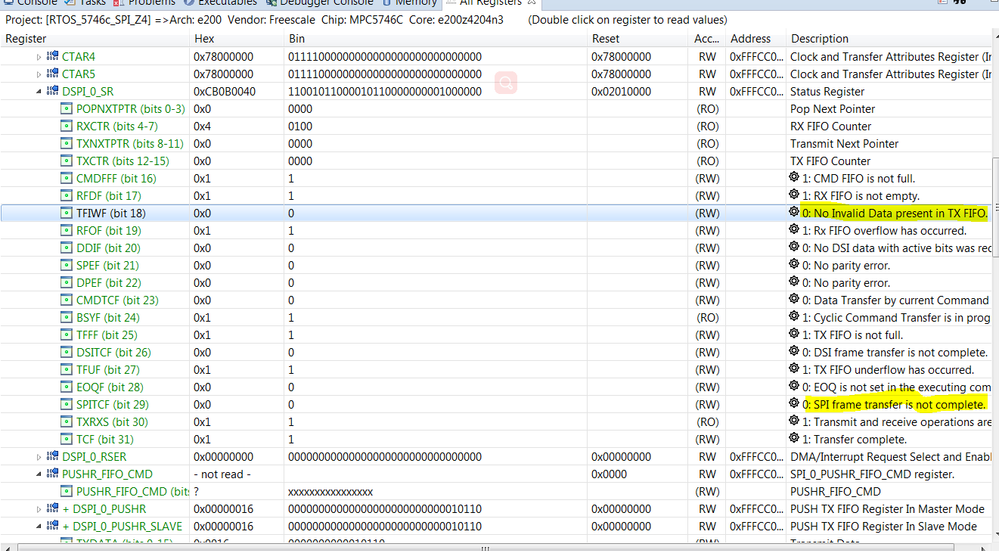

Above is the status register diagram of the attached project, RX&TX FIFO had overflow/underflow.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You send just 4 bytes because the CPU is not fast enough to push new data in TX FIFO. The transfer is interrupt by underflow event and the status of your transfer is fail.

To fix this behavior you have the following solutions:

-reduce spi master clock frequency

-use DMA mode

Best regards,

Razvan