- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Machine Check Exception occur with data cache enabled on MPC5746C multi-core project

Dear NXP team,

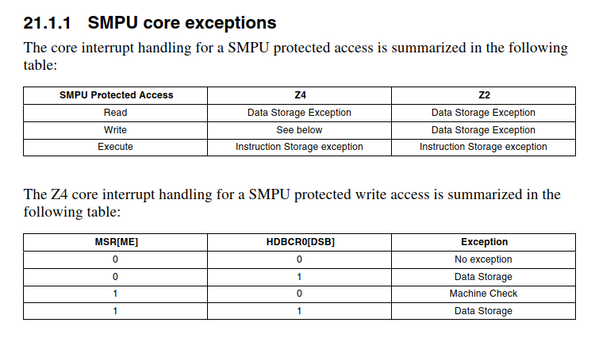

I am developing a multi-core project on MPC5746C, instruction cache and data cache of Z4 core is enabled at startup. To avoid cache coherency problem, SMPU is enabled and a region in system RAM is set as cache inhibited for inter-core communication. A machine check exception occurs with MAV/LD/BUS_RDERR set in MCSR, the example code of Z4 core and Z2 core are as follows:

/************************************

* Z4 core Code

***********************************/

#pragma ghs section data = ".NONE_CACHE_RAM" /*NONE_CACHE_RAM refers the cache inhibited region of SMPU*/

unsigned int z4_write_var = 1;

#pragma ghs section data = default

void test_code_z4(void)

{

while(1)

{

z4_write_var++;

}

}

/************************************

* Z2 core Code

***********************************/

extern unsigned int z4_write_var;

unsigned int z2_read_var;

void test_code_z2(void)

{

while(1)

{

z2_read_var = z4_write_var;

}

}

The running result of the program is that a machine check exception occurs, MAV/LD/BUS_RDERR are set in MCSR, and MCAR indicates the address of z4_write_var, I have checked .map file and I’m sure that z4_write_var locates within the cache inhibit region ".NONE_CACHE_RAM". And I have checked MEMU module, there is nothing indicating an ECC or EDC error.

I want to know what is the reason for the exception , and how to deal with it.

Looking forward for a reply!

Best Regards!

Victor

It should not be any difference between disabled cache and access to the SMPU region with cache inhibited attribute. Please check SMPU setting. Btw it is stated that aborted core accesses generate instruction storage (ISI) or data storage (DSI) interrupts, what would fit to described behavior.

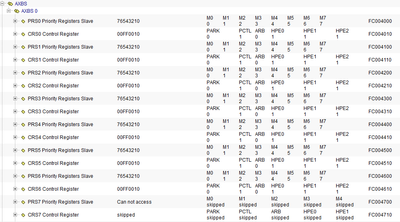

Sorry, I was on vacation these days. I have checked SMPU setting, there is no overlapping between SMPU regions, and the setting of the NON_CACHE_RAM is as follows:

REG_WRITE32(SMPU_0_RGD7_W2, 0xf3fcf000);

REG_WRITE32(SMPU_0_RGD7_W3, 0x00000002);

REG_WRITE32(SMPU_0_RGD7_W4, 0x00000000);

REG_WRITE32(SMPU_0_RGD7_W5, 0x00000001);

And I don't know what "aborted core accesses" is, would you please give me some special example.

The Error Status Register of SMPU did not imply any errors.

Does this problem have anything to do with the Store Buffer.

I just tried to disable the store buffer by the following code,

__MTSPR(976,0x00000008)

Then the program runs for 30 minutes with no error, I will test for longer time, I will update the test result to you tomorrow.

Thanks again for your help.

@lukaszadrapa @davidtosenovjan Sorry for bothering you, but would you please give me some advice to solve this problem?