- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi,

When we configure MPC5777C DSPI in 8-bit/16-bit mode, SOUT is pulsing exactly at 8th clock/16th clock pulse. Attached DSO screen yellow is SOUT (Highlighted with red circle), written data from MPC5777C is 0xA0 00 50 00 55, also attached DSPI configuration. Suggest how to solve this.

Thanks & Regards,

Sudheer A.

已解决! 转到解答。

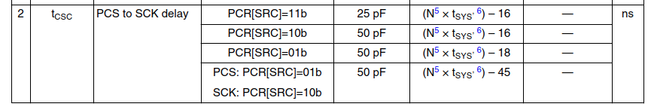

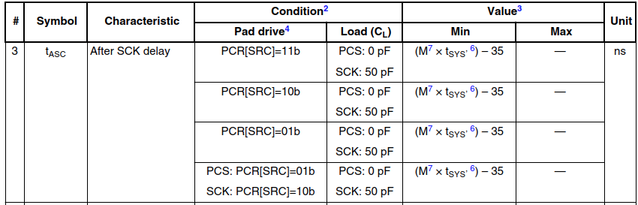

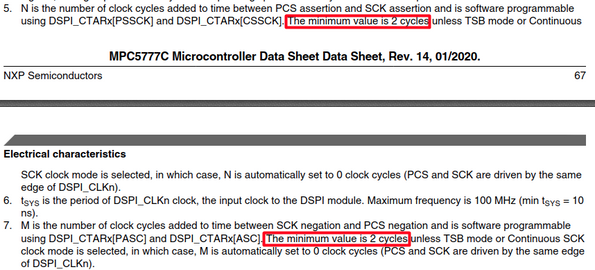

Such configuration is not possible. There is always certain minimum time between tASC/tCSC (as stated in the device datasheet), excluding mode with Continuous SCK.

You said "SLAVE doesn't require Continuous SCK" what does not imply such configuration cannot work. There is also CS signal that is being asserted only during transfer.

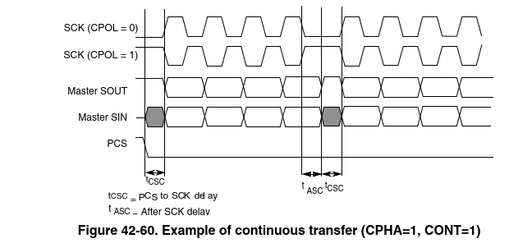

I think it is configuration like this:

Isn't it?

Can you zoom SCK signal below marked delays.

Actually what is the meaning of the question? Do you see some behavior contrary to the documentation description?

Such configuration is not possible. There is always certain minimum time between tASC/tCSC (as stated in the device datasheet), excluding mode with Continuous SCK.

You said "SLAVE doesn't require Continuous SCK" what does not imply such configuration cannot work. There is also CS signal that is being asserted only during transfer.

Here i have attached SLAVE communication which am trying to interface in same way from MPC5777C. DSO signals followed by CS, CLOCK, MOSI,MISO of proven SLAVE EVAL board communication. MOSI inactive state is low/high is acceptable.

Same couldn't match MPC5777C to SLAVE, because of tCSC and tASC .