- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

MPC5777C: wait instruction impact across cores

Hi,

I am working on MPC5777C and I have observed that when CPU1 is in wait state because of calling wait instruction; if CPU0 executes sync or syncm instruction it also stops. Can you please describe this behavior and is there any memory sync instruction which can avoid this behavior?

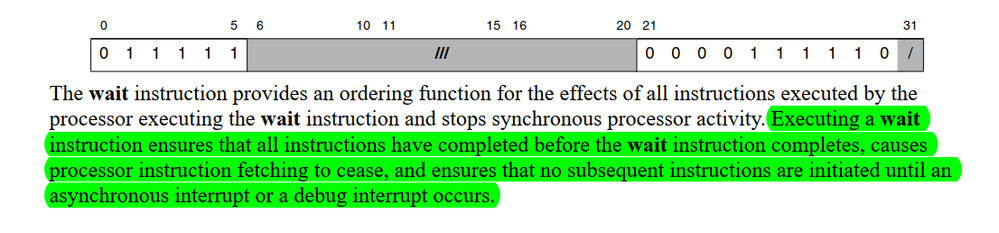

As per wait APU description;

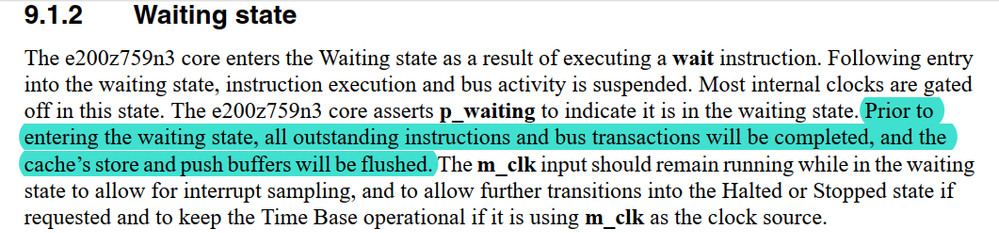

and waiting state;

So ideally CPU0 should not wait for any handshaking with CPU1.

-----------------------------------------------------------------------------------------

Related: MPC5777C: does Decrementer interrupt exit wait APU?

Hi,

please check the SIU_HLT1 register. The WAIT instruction can be configured to halt several peripherals, including both cores. If SIU_HLT[CORE0] is set, a WAIT instruction on core_1 would actually prevent the debugger from halting core_0.

If you are using WAIT, you have to make sure that there are any interrupts assigned (and actually occurring!) on that core. If not, then it will be stuck in WAIT and can never release any semaphores.

Best regards,

Reinhard

Hi,

I am using MPC5777C Cobra55 and observed this behavior. This behavior did not occur on other MPC targets like MPC5748G.

My use case is that core 1 is in idle mode of OS and OS use wait instruction in idle mode. So, when the other core (core 0) locks a semaphore and updates a shared variable (MMU is also On as per your first comment on Questions about Cache in the MPC5777C ), it then call sync instruction and this sequence happen more than once on core 0 while core 1 is in idle.

In this scenario a situation comes when core 0 also get stuck and even Lauterbach debugger can not call break on core 0 unless a break is executed on core 1. However it works perfect if OS do not use wait in it's idle mode.