- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5674F into slow mode

MPC5674F into slow mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5674F into slow mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I was wondering how it was possible to put the MPC5674F into `slow mode` like mentioned in the documentation:

1.2.2 Low-Power Modes

The MPC5674F includes two special modes to allow reduction of application power consumption:

• Stop mode: System clock stopped to all modules including the CPU. Wake-up timer used to restart

the system clock after a predetermined time.

• Slow mode: Allows the device to be run at very low speed (approximately 1 MHz), with modules

(including the PLL) selectively disabled in software.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't think such dedicated special mode would be there. It only mentions it is possible to configure clock to run down 1MHz, what's not common standard, but there is no dedicated 'slow' low power mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank,,

But I was wondering what are the PLL config to put it at 1MHz. Is it by using external clock???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

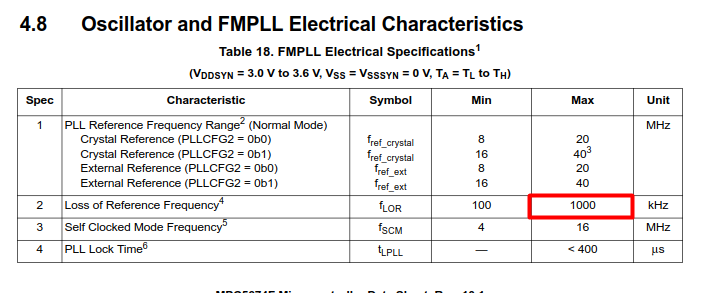

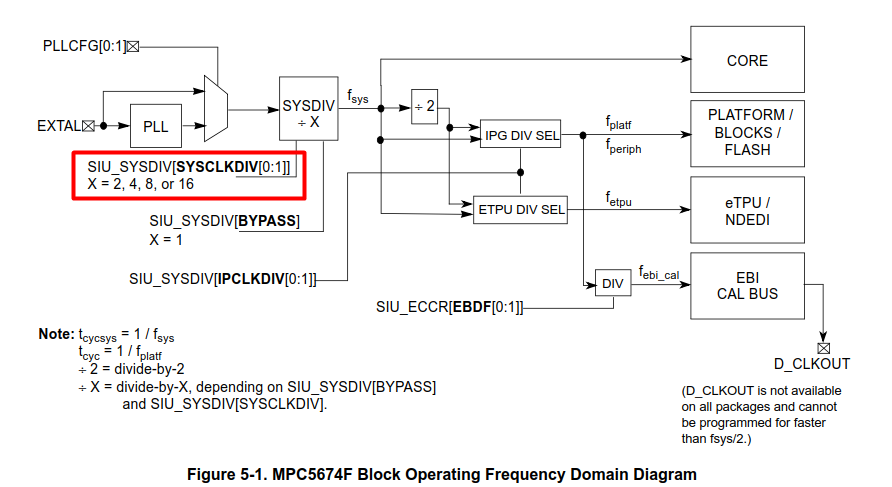

Either external or you use SYSCLKDIV divider. For instance you can setup PLL for 16MHz output (considering 16MHz crystal) and SYSCLKDIV for value of 16 => 1MHz system clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the info,

Do you know if this setting is used when we are using the JTAG. I am connecting through the JTAG to access memory (without init from the CPU).. How is the frequency computed then??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The recommended maximum JTAG frequency is 1/4th of the core frequency. (In this case 250kHz)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I understand the JTAG frequency is 1/4th of the core frequency, but the SIU_SYSCLKDIV is a register set at runtime or set once and will maintain its value after reset??

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

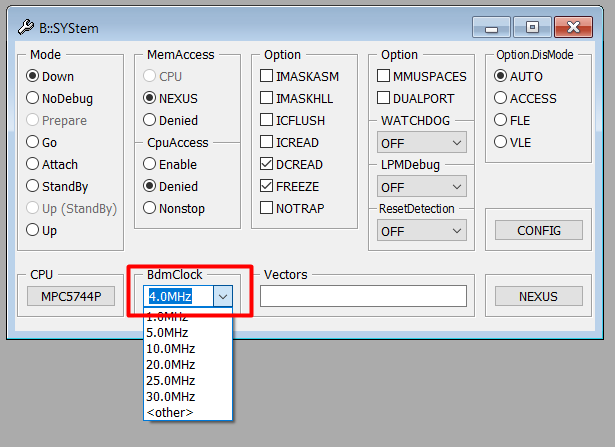

JTAG frequency is being set on the side of debugger, for instance here (considering TRACE32 debugger):

So it you change frequency significantly wanting to keep debugging during this "slow mode", you change this clock to keep 1/4th of the core frequency or you can have set for such slow clock for the whole time.