- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: Data not Receive properly in DSPI?

Data not Receive properly in DSPI?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Data not Receive properly in DSPI?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using S32 Design Studio.

S32 Design Studio for Power Architecture

Version: 1.2

Build id: 170613

(c) Copyright Freescale Semiconductor 2016. All rights reserved.

(c) Copyright NXP 2017.

MCU == MPC5777C

evb == MPC5777C EVB debugger == Multilink universal fx

Operating System == Win7x64,Win8x64 Case 1: System clock : 192 MHz(PLL0) DSPI module Clock : 96 MHz PER CLK SELECT : PLL0 PER CLK : 96 MHz SCK BAUD RATE : 4 MHz In this case the Data send on MOSI line is received properly on MISO line.Case 2: System clock : 264 MHz(PLL1)In both the case SCK baud rate is same which is derived from PER CLK but module clock is different. Is DSPI module clock has any effect on data send and receive functionality?DSPI module Clock : 132 MHzPER CLK SELECT : PLL0 PER CLK : 96 MHz SCK BAUD RATE : 4 MHz In this case the Data send on MOSI line is not received properly on MISO line.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

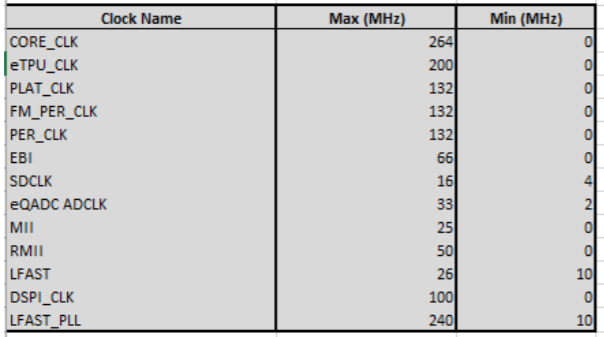

Hi, case 2 is out of maximum allowed DSPI frequency.

See datasheet screenshot below

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Here the maximum frequency 100 MHz which you are talking about is DSPI protocol clock which is generated from PER_CLK. My PER_CLK is 96 MHz for both above Cases which i referred.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

As per your suggestion i have changed the DSPI module clock to 66 MHz which is less than maximum 100 MHz frequency.

But still the problem remain same and i am not able to receive the data properly.

Thanks and Regards,

Sourabh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you shows details of this setting?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

here is system clock initialization of core clock 264 MHz.

System clock : 264 MHz(PLL1)

DSPI module Clock : 66 MHzvoid SystemClk_init(void)

{

PLLDIG.PLL0CR.B.CLKCFG = 0; // Disable PLL0

PLLDIG.PLL1CR.B.CLKCFG = 0; // Disable PLL1

SIU.SYSDIV.B.PLL0SEL= 0x0; // PLLOSEL = 0 The crystal oscillator (XOSC) is the clock source for PLL0

SIU.SYSDIV.B.PLL1SEL = 0x1; // PLL1SEL = 1 The PHI1 output of PLL0 is the clock source for PLL1

// configure PLL0 to 192 MHz (40 MHz XOSC reference)

//configure PLL1 to 264 MHz (48 MHz PLL0 PHI1 output reference)

/* Configure PLL0 Dividers - 160MHz from 20Mhz XTAL oscillator */

PLLDIG.PLL0DV.B.RFDPHI1 = 0x0C;

PLLDIG.PLL0DV.B.RFDPHI = 0x3;

PLLDIG.PLL0DV.B.PREDIV = 0x5;

PLLDIG.PLL0DV.B.MFD = 0x48;

/* Wait for stable XOSC */

SIU.RSR.B.XOSC = 0x1; //0 XOSC clock not stable yet

//1 XOSC clock is stable

/*Turn on PLL0 and wait for lock */

PLLDIG.PLL0CR.B.CLKCFG = 0x3; //Turn on PLL0

while(1)

{

if(PLLDIG.PLL0SR.B.LOCK == 0x01) // PLL is locked

break;

}

/* Configure PLL1 Dividers - 200MHz from 20Mhz XTAL oscillator */

PLLDIG.PLL1DV.B.RFDPHI = 0x02;

PLLDIG.PLL1DV.B.MFD = 0x16;

/*Turn on PLL1 and wait for lock */

PLLDIG.PLL1CR.B.CLKCFG = 0x3; //Turn on PLL0

while(1)

{

if(PLLDIG.PLL1SR.B.LOCK == 0x1) // PLL is locked

break;

}

/* Select clock dividers and sources */

SIU.SYSDIV.B.LCK = 0x0; // LCK = 0 SIU_SYSDIV register is unlocked and writes are permitted

SIU.SYSDIV.B.PLL0SEL= 0x0; // PLLOSEL = 0 The crystal oscillator (XOSC) is the clock source for PLL0

SIU.SYSDIV.B.PLL1SEL = 0x1; // PLL1SEL = 1 The PHI1 output of PLL0 is the clock source for PLL1

SIU.SYSDIV.B.PERCLKSEL = 0x1; // PERCLKSEL = 1 Clock is connected to the non-FM clock domain

SIU.SYSDIV.B.PERDIV = 0x0; // PERDIV = 0 Divide by 2.

SIU.SYSDIV.B.MCANSEL = 0x0; // MCANSEL = 0 The crystal oscillator (XOSC) is the clock source for the MCAN modules.

SIU.SYSDIV.B.SYSCLKSEL = 0x2; // SYSCLKSEL = 11 The system clock is driven by the non FM PLL (PLL0)

SIU.SYSDIV.B.FMPERDIV = 0x1;

SIU.SYSDIV.B.ETPUDIV = 0x1; // ETPUDIV = 1 Divide by 1.

SIU.SYSDIV.B.SYSCLKDIV = 0x4; // SYSCLKDIV = 100 Divide by 1

SIU.SYSDIV.B.PCSEN = 0x0; // PCSEN = 0 PCS disabled

SIU.ECCR.R =0x00000581;

SIU.SDCLKCFG.R = 0x0000000B;

SIU.LFCLKCFG.R = 0x00000001;

SIU.PSCLKCFG.R = 0x000100BF;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Whether you have seen following clock calculator. You may configure your clock settings by clicks and it checkes all frequency limits. In the summary tab, you may see configuration of all registers.

https://www.nxp.com/docs/en/application-note/AN12176.pdf

https://www.nxp.com/docs/en/application-note-software/AN12176SW.zip

Hope it helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I have checked the application note AN12176 which you have mention.

In that application note i have found out MPC5777C Frequency limits here snap is attached.

Here

FM_PER_CLK = 132 MHz (MAX) which drive the module clock of DSPI.

PER_CLK = 132 MHz (MAX) which drive Protocol clock of DSPI.

So right now i am using PER_CLK 96 MHz through which i derived SCK baud rate 4 MHz.

Case 1: System clock : 192 MHz(PLL0) DSPI module Clock : 96 MHz PER CLK SELECT : PLL0 PER CLK : 96 MHz SCK BAUD RATE : 4 MHz In this case the Data send on MOSI line is received properly on MISO line.Case 2: System clock : 264 MHz(PLL1)DSPI module Clock : 132 MHzPER CLK SELECT : PLL0 PER CLK : 96 MHz SCK BAUD RATE : 4 MHz In this case the Data send on MOSI line is not received properly on MISO line.

I have only changes the DSPI module clock which FM_PER_CLK from initially 96 MHz to 132 MHz and in this case my DSPI not working properly.

Why is this happening ?