- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- MCUXpresso软件和工具

- :

- MCUXpresso IDE

- :

- LPC54S018M CMSIS SPI driver error busy flag

LPC54S018M CMSIS SPI driver error busy flag

LPC54S018M CMSIS SPI driver error busy flag

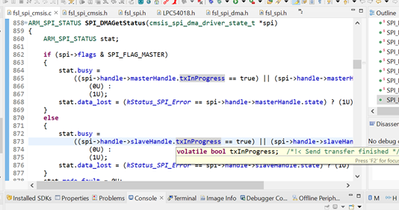

There seems to be an error in fsl_spi_cmsis.c in SPI_InterruptGetStatus(): To my mind the busy flag in the ARM_SPI_STATUS RETURN is set opposing to what I would expect. It will be set to "0" if there is still data to be transmitted or received.

(Same issue in SPI_GetDMAStatus() ..)

Hello @G1234,

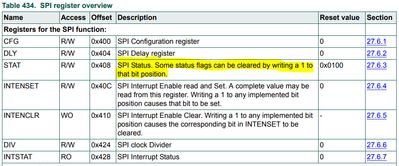

Related with the SPI_InterruptGetStatus(). If you look closely in the LPC540xx/LPC54S0xx User manual; Chapter 27: LPC540xx/LPC54S0xx Serial Peripheral Interfaces (SPI); you will see that the SPI Status register (STAT), specifies that some flags actually can be cleared by writing a 1.

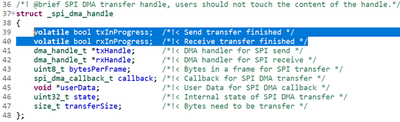

And related with the SPI_GetDMAStatus(), if you click or let the cursor in txInProgress or rxInProgress, you will be able to see that actually the flag is setting with a 1 when the transfer is active (busy), and clearing with a 0, when the transfer ends.

Regards, Raul.

Hello Paul,

thank you for looking at this.

But I still think that in both of the "getStatus"-Routines SPI_InterruptGetStatus() and SPI_DMAGetStatus() the stat.busy flag returns just the opposite: The code says

"if either TX is in progress OR RX is in progress the SPI is not busy" (stat.busy is set to 0)

according to your explanation and my understanding it should be:

"if either TX is in progress OR RX is in progress the SPI is busy" (stat.busy should be set to 1)

(This is not a question about how to clear the flags in the registers of the processor)

Hello @G1234,

I apologize for the misunderstanding. The stat.busy in both functions GetStatus (DMA and Interrupt) is setting to 0 when SPI is busy.

- (SPI_InterruptGetStatus)txRemainingBytes and rxRemainingBytess will decrease its value until it ends the transfer.

- (SPI_DMAGetStatus)txInProgress and rxInProgress will be True during the transfer, and False only when the transfer ends or aborts.

So, as you say, stat.busy will be 0 while SPI communicates, and 1 when doesn't.

Best regards, Raul.