- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- レイヤースケープ

- :

- Re: CWTAP connection failed when using CW to debug LS1043A

CWTAP connection failed when using CW to debug LS1043A

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I am using CW to debug LS1043ardb, and CWTAP is used.

After building source code, and trying to debug the application on the board, I will met below error when dowloading:

Errors in Debug Server

---------------------------------

Target connection failed. Please re-check the settings.

//

Processor: LS1043A

Probe: //

Additional error details:

[CCS: subcore error during multicore operation]

I am using the default LS1043A_RDB target connection configuration which is provided in CW. version of CW is:

CodeWarrior Development Studio for QorIQ LS series - ARM V8 ISA

(c) Freescale Semiconductor, Inc. 2014. All rights reserved.

Learn more about CodeWarrior at

http://www.freescale.com/codewarrior

Version: 11.2.0

Build Id: 160115

Also I tried to run "source IDcode.tcl" on ccs, below is the output:

(bin) 57 % source IDcode.tcl

Scanning for available TAPs connected via USB.....

++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

+

+ Available Remote Connections

+

+ 1 - CodeWarriorTAP - 00:04:9f:03:ae:f8

+ 2 - CodeWarriorTAP - <Specify IP Address>

+ 3 - GigabitTAP - <Specify IP Address>

+

+ x - Exit Script without Changes

+

++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Specify connection:

1

Configuring TAP Interface....

Configured Connection: cwtap : 00:04:9f:03:ae:f8

TDO -----

|

* Device 0 IDCODE: 5BA00477 Device: Unknown Device

* Device 1 IDCODE: 06B1001D Device: Unmapped FSL Device

|

TDI -----

###################################################

#

# configTAP - Redefine TAP interface

#

# scanboard - Scans the target system

# and returns the JTAG IDCode

#

# ir - Loopback test

#

###################################################

Please help to have a look what's the problem. Thank you very much.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

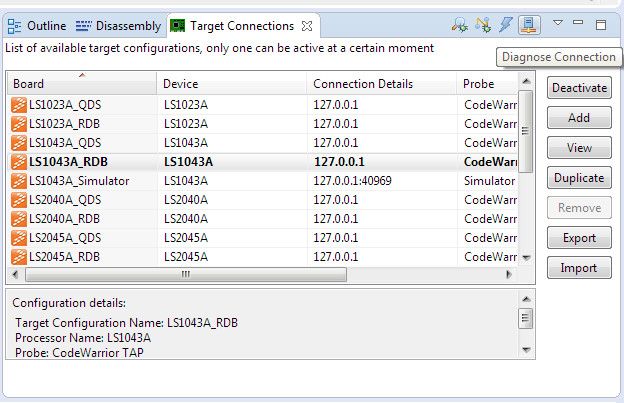

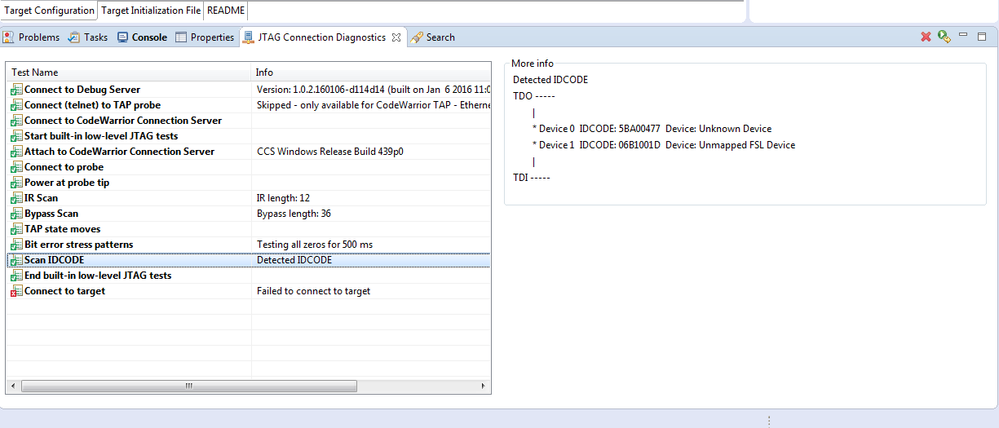

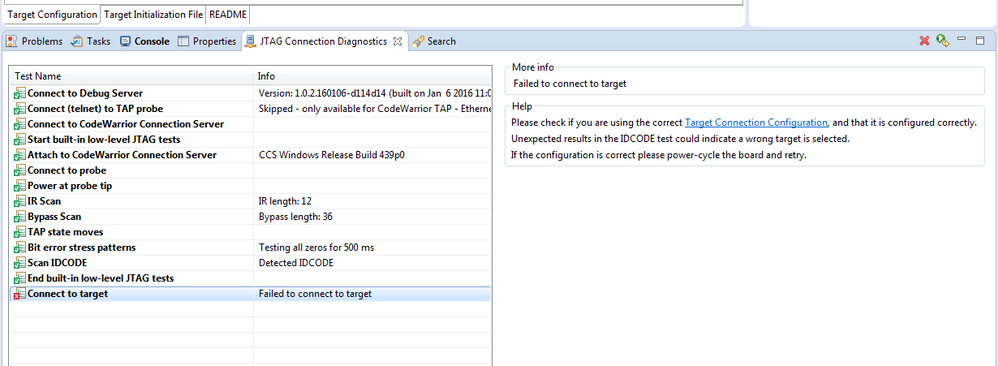

This is the diagnose result, please help to have a look.

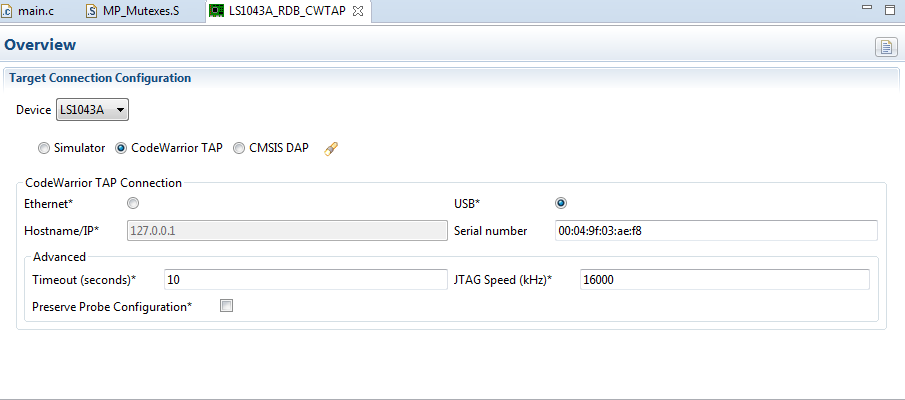

Also, the connection configuration is:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please try to modify the LS1043A_RDB Target Initialization File in the Main change the line:

useSafeRCW = False

to

useSafeRCW = True

and run "Diagnose Connection"

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

After that change, I will meet this problem when "connect":

Errors in Debug Server

---------------------------------

Target connection failed. Please re-check the settings.

//

Processor: LS1043A

Probe: CodeWarrior TAP (00:04:9f:03:ae:f8)

//

Additional error details:

[GTA: all targeted cores are in unsupported aarch32 mode]

"diagnose connection" will return same result as I attached in last reply.

BTW, the initialization file content is like below:

python

###################################################################

# Copyright (C) 2015, Freescale Semiconductor, Inc.

# All Rights Reserved

###################################################################import gdb

import time

import ctypesCORE_CONTEXT = ":ccs:LS1043A:CortexA53#0"

###################################################################

# Utility functions

####################################################################This function should be used instead of gdb.execute in all cases when the value returned is used in the script

def gdb_exec(command, from_tty, to_string):

"""Execute a gdb command, remove the echo if it appears, handle the exception"""

try:

string = gdb.execute(command, from_tty, to_string)

echo_command = "+++" + command + "\n"

if string is not None and string.startswith(echo_command):

return string[len(echo_command):]

else:

return string

except StandardError as msg:

print("\nError when executing gdb command: " + command)

print(msg)

return None# Swap utility function

def Swap32(x):

return (((x << 24) & 0xFF000000) |

((x << 8) & 0x00FF0000) |

((x >> 8) & 0x0000FF00) |

((x >> 24) & 0x000000FF))# Memory Modify

def MM(context, address, accessSize, space, value):

gdb.execute("monitor mem write %s %#x %d %s %#x" % (context, address, accessSize, space, value))

return# Memory Display

def MD(context, address, accessSize, space):

return int(gdb_exec("monitor mem read %s %#x %d %s 1" % (context, address, accessSize, space), False, True), 16)# CCSR BigEndian Modify

def CCSR_BE_M(address, value):

MM(CORE_CONTEXT, address, 4, "physical_noncoherent", value)

return# CCSR BigEndian Display

def CCSR_BE_D(address):

return MD(CORE_CONTEXT, address, 4, "physical_noncoherent")# CCSR LittleEndian Modify

def CCSR_LE_M(address, value):

return CCSR_BE_M(address, Swap32(value))# CCSR LittleEndian Display

def CCSR_LE_D(address):

return Swap32(CCSR_BE_D(address))# Register Modify

def RM(context, registerId, size, value):

gdb.execute("monitor reg write %s %#x %d %#x" % (context, registerId, size, value))

return# Register Display

def RD(context, registerId, size):

return int(gdb_exec("monitor reg read %s %#x %d" % (context, registerId, size), False, True), 16)# Template Config

def TMP_CFG(context, reg, data):

gdb.execute("monitor template config %s %#x %#x" % (context, reg, data))

return

###################################################################

# Reset

###################################################################

def Reset(useSafeRCW):

if useSafeRCW:

# Set rcw_src to hard-coded RCW option

gdb.execute("monitor rcw source set 0x9F")

# add here if you need to override other particular RCW values

# gdb.execute("monitor rcw data set RCW1 0x40282830 RCW9-10 0x00C12980 0x00002580")

gdb.execute("monitor rcw apply")else:

try:

# This init requires target reset, irrespective of the user preference

#user_reset = gdb.parse_and_eval ("$reset")

userResetDelay = int(gdb.parse_and_eval ("$delay"))

except gdb.error:

userResetDelay = 0

gdb.execute("py-reset %d" % userResetDelay)# RCPM_CESRD sticky bit which will get set when you deassert EVT_B0

# REMOVE EXTERNAL DEBUG REQUEST which we issue in ccs on ccs::reset_to_debug

CCSR_BE_M(0x20160704, 0x80000000)

CCSR_BE_M(0x20160708, 0x80000000)

CCSR_BE_M(0x2016070C, 0x80000000)# Safeguard against reset skid on CMSISDAP

# Clear PC

RM(CORE_CONTEXT, 0x1DA29, 8, 0)

# Clear MMU, caches, aligment checks, WNX in SCTLR_EL3

SCTLR_EL3 = RD(CORE_CONTEXT, 0x1F080, 4)

SCTLR_EL3 = SCTLR_EL3 & 0xFFF7EFF0

RM(CORE_CONTEXT, 0x1F080, 4, SCTLR_EL3)return

###################################################################

# CCI Initialization

###################################################################

def Init_CCI():

# Set Terminate all barrier transactions bit of CCI-400 Control Register

# (needed for dsb instruction to succeed when doing coherent reads/writes)

# It will be disabled after DDR is initialized

CCSR_LE_M(0x01180000, 0x00000008)# Enable snoop requests and DVM messages for A53 cluster slave interface 4

CCSR_LE_M(0x01185000, 0x00000003)return

###################################################################

# Boot Release

###################################################################

def Init_BRR():

# TODO: when we can detect the current context,

# release all cores for SMP, current core for AMP# Write to BRR to release cores

CCSR_BE_M(0x1EE00E4, 0x0000000F)return

###################################################################

# DDR Initialization

###################################################################

def Init_DDRC():

# SDRAM_CFG

CCSR_BE_M(0x1080000 + 0x110, 0x450C000C)# CS0_BNDS

CCSR_BE_M(0x1080000 + 0x000, 0x0000007f)

# CS0_CONFIG

CCSR_BE_M(0x1080000 + 0x080, 0x80010322)# TIMING_CFG_0

CCSR_BE_M(0x1080000 + 0x104, 0xD0550018)

# TIMING_CFG_1

CCSR_BE_M(0x1080000 + 0x108, 0xC2C68C42)

# TIMING_CFG_2

CCSR_BE_M(0x1080000 + 0x10C, 0x0048C114)

# TIMING_CFG_3

CCSR_BE_M(0x1080000 + 0x100, 0x020C1000)

# TIMING_CFG_4

CCSR_BE_M(0x1080000 + 0x160, 0x00000002)

# TIMING_CFG_5

CCSR_BE_M(0x1080000 + 0x164, 0x04401400)

# TIMING_CFG_7

CCSR_BE_M(0x1080000 + 0x16C, 0x13300000)

# TIMING_CFG_8

CCSR_BE_M(0x1080000 + 0x250, 0x03115600)# SDRAM_CFG_2

CCSR_BE_M(0x1080000 + 0x114, 0x00401010)# SDRAM_MODE

CCSR_BE_M(0x1080000 + 0x118, 0x01010214)

# SDRAM_MODE_2

CCSR_BE_M(0x1080000 + 0x11C, 0x0)# SDRAM_INTERVAL

CCSR_BE_M(0x1080000 + 0x124, 0x18600618)# DDR_WRLVL_CNTL

CCSR_BE_M(0x1080000 + 0x174, 0x8655F606)# DDR_WRLVL_CNTL_2

CCSR_BE_M(0x1080000 + 0x190, 0x05070600)

# DDR_WRLVL_CNTL_3

CCSR_BE_M(0x1080000 + 0x194, 0x0)# DDR_CDR1

CCSR_BE_M(0x1080000 + 0xB28, 0x80040000)

# DDR_CDR2

CCSR_BE_M(0x1080000 + 0xB2C, 0x0000A181)# SDRAM_CLK_CNTL

CCSR_BE_M(0x1080000 + 0x130, 0x02000000)

# DDR_ZQ_CNTL

CCSR_BE_M(0x1080000 + 0x170, 0x8A090705)# SDRAM_MODE_9

CCSR_BE_M(0x1080000 + 0x220, 0x00000400)

# SDRAM_MODE_10

CCSR_BE_M(0x1080000 + 0x224, 0x04000000)# CS0_CONFIG_2

CCSR_BE_M(0x1080000 + 0x0C0, 0)# SDRAM_CFG

CCSR_BE_M(0x1080000 + 0x110, 0xC50C000C)# Poll for DDR to be initialized

count = 0

while True:

time.sleep(0.2)

SDRAM_CFG2 = CCSR_BE_D(0x01080114)

D_INIT = SDRAM_CFG2 & 0x10

count = count + 1

if (D_INIT == 0):

break

if (count > 20):

print "DDRC: Time out waiting for D_INIT"

breakERR_DETECT = CCSR_BE_D(0x01080E40)

if (ERR_DETECT != 0):

print "Memory initialization error on DDRC!"

print format(ERR_DETECT, '08x')time.sleep(1)

# Clear Terminate all barrier transactions bit of CCI-400 Control Register

CCSR_BE_M(0x01180000, 0x00000000)return

###################################################################

# IFC Initialization

###################################################################

def Init_IFC():

# Reset IFC

# GCR

CCSR_BE_M(0x0153040C, 0x8000F000)

time.sleep(0.1)

CCSR_BE_M(0x0153040C, 0x0000F000)

# Poll for reset to finish

count = 0

while True:

time.sleep(0.2)

GCR = CCSR_BE_D(0x0153040C)

SOFT_RESET = GCR & 0x80000000

count = count + 1

if (SOFT_RESET == 0):

break

if (count > 20):

print "IFC: Time out waiting for soft reset"

break# CCR

CCSR_BE_M(0x0153044C, 0x04008000)

# Poll for stable clock

count = 0

while True:

time.sleep(0.2)

CSR = CCSR_BE_D(0x01530450)

count = count + 1

if ((CSR & 0x80000000) != 0):

break

if (count > 20):

print "IFC: Clock not stable"

breakNOR_CS = 0

NAND_CS = 1# Check IFC_CSPR0. CPLD Chip select is assumed to be always 2.

CSPR0 = CCSR_BE_D(0x1530010)

# Check MSEL to see if NAND is on CS 0, otherwise assume NOR.

if ((CSPR0 & 0x7) == 0x3):

NOR_CS = 1

NAND_CS = 0# CSPR_EXT

CCSR_BE_M(0x0153000C + NOR_CS * 12, 0x00000000)

# CSPR

CCSR_BE_M(0x01530010 + NOR_CS * 12, 0x60000101)

# AMASK

CCSR_BE_M(0x015300A0 + NOR_CS * 12, 0xF8000000)

# CSOR

CCSR_BE_M(0x01530130 + NOR_CS * 12, 0x0000800C)# IFC_FTIM0

CCSR_BE_M(0x015301C0 + NOR_CS * 48, 0x1001000C)

# IFC_FTIM1

CCSR_BE_M(0x015301C4 + NOR_CS * 48, 0x1C000B09)

# IFC_FTIM2

CCSR_BE_M(0x015301C8 + NOR_CS * 48, 0x01102010)

# IFC_FTIM3

CCSR_BE_M(0x015301CC + NOR_CS * 48, 0x00000000)# CSPR_EXT

CCSR_BE_M(0x0153000C + NAND_CS * 12, 0x00000000)

# CSPR

CCSR_BE_M(0x01530010 + NAND_CS * 12, 0x7E800083)

# AMASK

CCSR_BE_M(0x015300A0 + NAND_CS * 12, 0xFFFF0000)

# CSOR

CCSR_BE_M(0x01530130 + NAND_CS * 12, 0x85082100)# IFC_FTIM0

CCSR_BE_M(0x015301C0 + NAND_CS * 48, 0x0E18070A)

# IFC_FTIM1

CCSR_BE_M(0x015301C4 + NAND_CS * 48, 0x32390E18)

# IFC_FTIM2

CCSR_BE_M(0x015301C8 + NAND_CS * 48, 0x01E0501E)

# IFC_FTIM3

CCSR_BE_M(0x015301CC + NAND_CS * 48, 0x00000000)return

###################################################################

# Adds Flash devices for this board

###################################################################

def Config_Flash_Devices():

# Add NOR device

gdb.execute("monitor flash device alias nor name MT28EW01 address 0x60000000 ws_address 0x10000000 ws_size 0x1FFFF geometry 16x1 controller IFC")# Add NAND device

gdb.execute("monitor flash device alias nand name MT29F4G08ABBDAv1 address 0x7E800000 ws_address 0x10000000 ws_size 0x1FFFF geometry 8x1 controller IFC")# Add SD/eMMC device

gdb.execute("monitor flash device alias sd name SDSP16GB_LSCH2 address 0x00000000 ws_address 0x80000000 ws_size 0x1FFFF geometry 8x1 controller IFC")#set nor as current device

gdb.execute("monitor flash current nor")return

###################################################################

# Main

#################################################################### Uncomment to enable RCW override

useSafeRCW = True

Reset(useSafeRCW)Init_CCI()

Init_IFC()

Init_DDRC()

Init_BRR()

Config_Flash_Devices()

end

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In the future please attach big texts instead of "inline".

Is the board capable to boot?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your reminder ufedor.

Root cause is that I didn't stop the U-Boot count down, and the board goes to a 32-bit Linux kernel before my debug.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please run "Diagnose Connection" and provide the log