- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

Hi, I set up a DMA to transfer data over I2S.0 in my lpc4337. Alsignals look OK (SCK, WS and SD), but the MCLK signal is only 1v, and it does NOT look square at all.

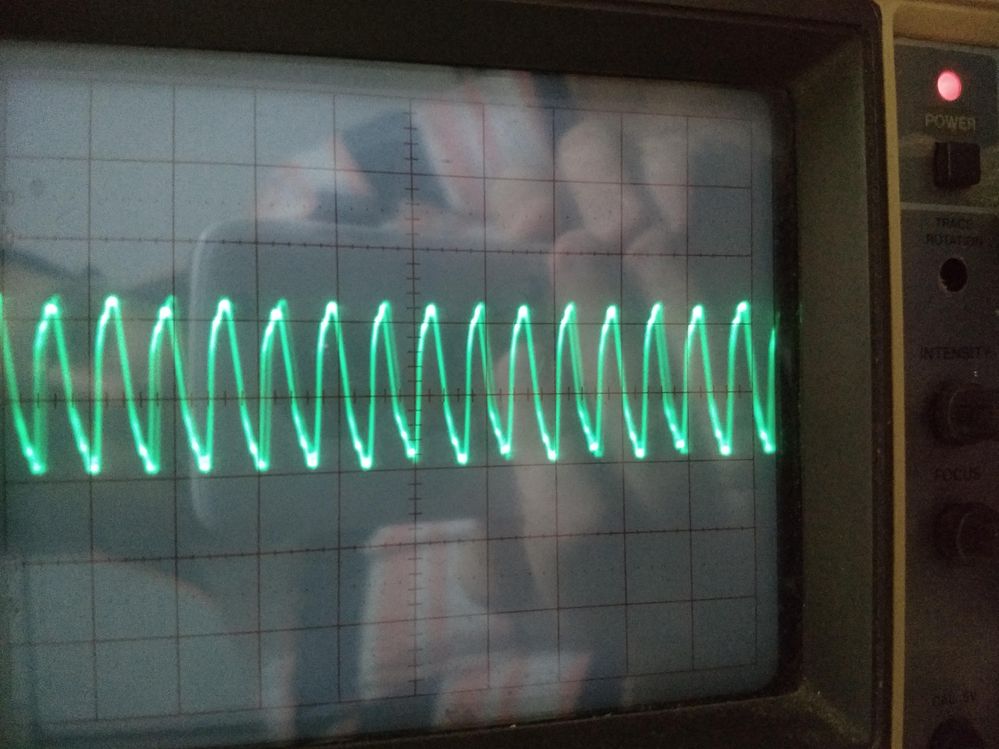

This is the output of a 20Mhz the oscilloscope I have at home:

500mV x 0.2uS

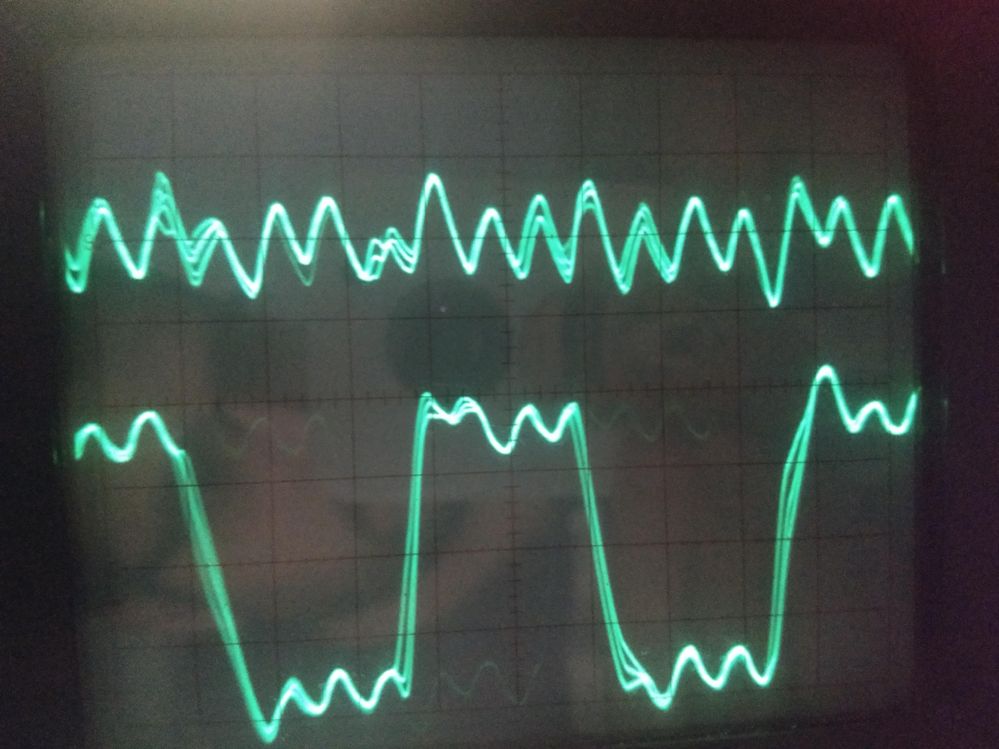

mclk signal is about 5mm of distance from the board pin and it can't get any closer. I used to have a protoboard with a lot of long cables, and the signal looked like the one below, but that's no longer the case.

MCLK and SCK with very long cables on a protoboard. 1V x 0.2uS.

Ignore this picture as this is no longer a problem.

Any tips on what may be going on?

I2S extra question

CS4335 protocol is i2s, left justified, MSB first. From their datasheet the data is valid on the first rising edge.

About shifting the bits with respect to frame edges. I believe this is called PCM typical format, while NOT shifting the bits is the typical i2s protocol. Out of curiosity, is there any way to do this in the LPC4337? And about being left justified, is there any way to set it up? Because I've been reading the Datasheet but I'm not able to find it.

So far I had to modify LPC open to change to big endianess, and enable MCLK, which was not possible with the existing examples.

Nevertheless the main issue for now is that I'm not being able to output a clean MCLK to power on the CS4335 as it requires MCLK and WS to power ON. (SCK is optional).

Thank you.

已解决! 转到解答。

Hi, Emilio,

Yes, the LPC4337 supports the standard I2S mode(Bits are right shifted by one with respect to frame edges), I also checked the data sheet of CS4334-5-8-9-F7.pdf, the Figure 10. CS4334 Data Format (I²S) means that only CS4334 supports the standard I2S mode.

Hope it can help you

BR

Xiangjun Rong

Hi, Emilio,

Regarding the question that "the MCLK signal is only 1v, and it does NOT look square at all.", it appears that the Oscilloscope bad pass-band leads to the issue for example distort and low voltage, maybe the original signal is okay. If possible, can you use another digital oscilloscope to have a test?

I have downloaded the data sheet of CS4335, the codec supports both modes: Frame signal with one-bit shift early or frame signal without one-bit shift early modes. Pls refer to Figure 10. CS4334 Data Format (I²S) and Figure 11. CS4335 Data Format in DS of CS4335. For the LPC4337, I think it only supports the standard I2S mode that the Frame signal is of one-bit shift early.

Hope it can help you

BR

XiangJun Rong

Hi, thanks for the reply. I will assume my oscilloscope is not showing the right voltage for such high frequencies.

With that in mind, I can see two things:

1) Looking at the logic analyzer I can confirm the LPC 4337 sends the data in i2s standard format. Bits are right shifted by one with respect to frame edges

2) Only the CS4334 supports standard i2s format(shifted). The CS4335 expects the bits in PCM standard format (not shifted).

Since there is no way for the LPC4337 to output data in PCM standard format (I didn't find it in the User Manual UM10503), I can conclude it's compatible with the CS4334, but NOT with the CS4335.

Is this correct?

Thank you,

Hi, Emilio,

Yes, the LPC4337 supports the standard I2S mode(Bits are right shifted by one with respect to frame edges), I also checked the data sheet of CS4334-5-8-9-F7.pdf, the Figure 10. CS4334 Data Format (I²S) means that only CS4334 supports the standard I2S mode.

Hope it can help you

BR

Xiangjun Rong