- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC5536 - I3C ENTDAA - R-START issue

LPC5536 - I3C ENTDAA - R-START issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC5536 - I3C ENTDAA - R-START issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone!

I'm working on an I3C driver for LPC5536 MCU for a client. Until now, I am working on Master SDR support, and Private Read, Private Write, CCC commands, and I2C over I3C are already implemented and running perfectly.

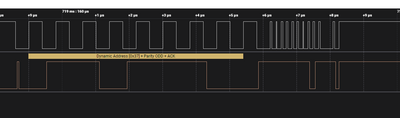

The problem is that ENTDAA is not working well. After the first dynamic address is assigned to the first target, the R-START condition is not performed correctly and is not recognized by the rest of the targets. Attached is a picture.

I found another post here (https://community.nxp.com/t5/i-MX-Processors/I3C-ENTDAA-Repeated-start-waveform/m-p/1387045). I copyed the timing characteristics (Ton for PP, etc, etc) but the problem is still present. I tried enabling ODHPP, disabling ODHPP, respecting 200 ns for Open-Drain Ton period, but nothing solve the problem.

In my case, the I3C Clk Freq is 50 MHz, after dividing the main clock 150 MHz by 3.

Do you have any suggestion??

BR,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @xiangjun_rong,

I'm still waiting for a new response from you. This looks like a JOKE. I'm working hard on a project with the MCUs LPC5536 and LPC5534 supporting I3C capability. I've been working seriously on this project for 6 months, and the support from your team regarding this issue is terrible, it is so bad...a complete disaster.

You can see that I have a bunch of tickets opened all those related to I3C peripheral and MCU documentation (that is really poor and bad too). So, please, take this issue important! I need your help to solve this issue, but I want to cooperate too.

I'm working on an I3C event-driven driver, because the one that is included in the SDK is not working properly. It polls a lot of flags instead of work by events.

Please, I need to solve this issue. It's important for me.

@CarlosGarabito , you have responded my last tickets. Could you help me to get a better assistance here, please? I apologize for tagging you in this ticket, but the assistance here has been a disaster, and perhaps you can help me.

Beset regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjun_rong,

How is it going?

Can you give me a new response, please?

As I said before, I want to cooperate and I need to solve this problem, but this conversation is really slow.

High SCL frequencies are being also a bit chaotic, so I need to progress with these issues.

Waiting for a response ASAP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjun_rong,

Have you got any news?? Could you open the captures? Let me know if you want my code to reproduce in your testbench.

BR,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let me know if you prefer that I share the code that I am using to test it by yourself.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I share my last tests...

- I kept I3C FCLK 50 MHz

- I kept PPBAU = 1

- I changed ODHPP to 0.

- I tested OD SCL Frequency to 1.25 MHz and 2.5 MHz to ensure that the First I3C Boradcast Address 0x7E Open Drain timing contrains are satisfied (both SCL Low Period and SCL High Period greater than 200 ns)

In these cases the Boradcast 0x7E is ACKed, (Broadcast ENEC and Broadcast RSTDAA are performed first), so ENTDAA starts correctly, the first target sends PID, BCR and DCR, the controller assigns a dynamic address but fails in the R-START pattern.

Attached are these two captures plus the one I sent above. I changed the names to identify each case. The captures sample rate is 100 Mb/s, generated with Saleae Logic 2.

Please let me know if you need further information.

BR,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well... I did one more test. I kept FCLK in 50 MHz and incremented PPBAUD from 1 to 2 so now the SCL T high is greater than 50 ns. However the 0x7E is NACKed yet, while SCL T high is 70 ns.

Attached is the capture I shared in the last reply and the new one that shows what I'm reporting here.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is SDK example "lpcxpressolpc55s36_i3c_master_read_sensor_icm42688p" in SDK package based on LPC55S36.

In the example code, this is an api function

result = I3C_MasterProcessDAA(EXAMPLE_MASTER, addressList, sizeof(addressList));

Pls run the code and check the result of the above function. The function executes ENTDAA and read 8 bytes data from target.

Hope it can help you

BR

XiangJun Rong

int main(void)

{

i3c_master_config_t masterConfig;

status_t result = kStatus_Success;

/* attach 12 MHz clock to FLEXCOMM0 (debug console) */

CLOCK_SetClkDiv(kCLOCK_DivFlexcom0Clk, 0u, true);

CLOCK_SetClkDiv(kCLOCK_DivFlexcom0Clk, 1u, false);

CLOCK_AttachClk(BOARD_DEBUG_UART_CLK_ATTACH);

/* Attach main clock to I3C, 150MHz / 4 = 37.5MHz. */

CLOCK_SetClkDiv(kCLOCK_DivI3cFclk, 0U, true);

CLOCK_SetClkDiv(kCLOCK_DivI3cFclk, 4U, false);

CLOCK_AttachClk(kMAIN_CLK_to_I3CFCLK);

BOARD_InitPins();

BOARD_BootClockPLL150M();

BOARD_InitDebugConsole();

PRINTF("\r\nI3C master read sensor data example.\r\n");

I3C_MasterGetDefaultConfig(&masterConfig);

masterConfig.baudRate_Hz.i2cBaud = EXAMPLE_I2C_BAUDRATE;

masterConfig.baudRate_Hz.i3cPushPullBaud = 12500000U;

masterConfig.baudRate_Hz.i3cOpenDrainBaud = 4000000U;

masterConfig.enableOpenDrainStop = false;

I3C_MasterInit(EXAMPLE_MASTER, &masterConfig, I3C_MASTER_CLOCK_FREQUENCY);

I3C_MasterTransferCreateHandle(EXAMPLE_MASTER, &g_i3c_m_handle, &masterCallback, NULL);

i3c_register_ibi_addr_t ibiRecord = {.address = {SENSOR_ADDR}, .ibiHasPayload = true};

I3C_MasterRegisterIBI(EXAMPLE_MASTER, &ibiRecord);

PRINTF("\r\nI3C master do dynamic address assignment to the sensor slave.\r\n");

uint8_t addressList[1] = {SENSOR_ADDR};

result = I3C_MasterProcessDAA(EXAMPLE_MASTER, addressList, sizeof(addressList));

if (result != kStatus_Success)

{

return -1;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjun_rong, thanks for your response.

I ran the SDK example as you asked. But I didn´t get a good result. Most of the time, the example starts the ENTDAA correctly but it gets halted after sending the dynamic address. Attached is a capture from Saleae Logic that shows this.

One thing I did was read/get MCONFIG register to analyze the peripheral configuration.

The details are:

- MCU Clock set to 150 MHz.

- I3C Clock set to 37.4 (I3C Clock divider set to 4)

- PPBAUD = 1 ( So Push-Pull SCL T high = 53.33 ns)

- PPLOW = 0 ( So Push-Pull SCL Frequency is 9.375 MHz)

- ODHPP = 1 ( So Open-Drain SCL T high = Push-Pull SCL T high)

- ODBAUD = 3 ( So Open-Drain SCL Frequency is 3.75 MHz)

- HKEEP = 0

- ODSTOP = 0

- SKEW = 0

I tryed to follow a similar configuration:

- MCU Clock set to 150 MHz.

- I3C Clock set to 50 MHz (I3C Clock divider set to 3)

- PPBAUD = 1 to get Push-Pull SCL High 40 ns.

- PPLOW takes the values:

Fclk [MHz] 50 PPBAUD 1 PPLOW SCL(MHz) 0,0 12,50000 1,0 10,00000 4,0 6,25000 6,0 5,00000 12,0 3,12500 - ODHPP = 1 ( So Open-Drain SCL T high = Push-Pull SCL T high) Keep the example config here.

- ODBAUD = 6 ( So Open-Drain SCL Frequency is 3.125 MHz)

- HKEEP = 0

- ODSTOP = 0

- SKEW = 0

As result, in my case the first I3C Broadcast Address 0x7E is NACKed. There is a Salae Logic attached too.

Some observations here:

- I understand that the first I3C Broadcast Address should be performed in Open-Drain. This seems to occur in my project, however seems like in the SDK example the first 0x7E is performed in push-pull because the SCL frequency is closer to Push-Pull frequency than the Open-Drain frequency. 10 MHz is too high for Open-Drive or unless is not allowed in I3C MIPI specification. Refer to Table 86 I3C Open Drain Timing Parameters on MIPI I3C Basic V1.1.1 specification. However, it seems to work because the 0x7E was ACKed.

- The fact that the first 0x7E is NACKed in my case, might be due to a short SCL T high equal to 40 ns. Could be possible that an I3C target that has no dynamic address assigned might have the 50 ns spike filter activated so it doesn't detect the I3C traffic. In the SDK example the SCL T high is equal to 60 ns which is greater than 50 ns. However the Table 86 I3C Open Drain Timing Parameters on MIPI I3C Basic V1.1.1 specification, indicates that in Open-Drain minimum High Period of SCL is should be 200 ns for this purpose.

- The Table 86 I3C Open Drain Timing Parameters on MIPI I3C Basic V1.1.1 specification, indicates that in Open-Drain minimum Low Period of SCL is always 200 ns. This is not true in the SDK example.

Regarding point number 2, I remember that I tested ODHPP = 1 and SCL T high greater that 50 ns before opening this ticket. I remember I got the 0x7E ACKed but the problem with the R-START persisted.

In this link to GSheet I wrote some combinations from the CLK configuration. You will find the SDK configuration and other possible configurations. Please see the tab called "Analysis". I'd be gratefull if you review and confirm that the calculus are correct.

Finally, I am really interested in collaborate to solve this problem. I am working with I3C since 2021 and I love it. I am working now in an important project for a client and my experience hasn't been too good working with the LPC55S36 and I3C peripheral.

Let me know if you need further information.

Looking forward for your comments.

BR,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi! I would like to receive a response or any comment ASAP. I am going on with the project on wich I am working but I need to fix this issue.

Thanks in advance!

PS. I have some comments regarding the documentation. I think I found other doc errors, so I will open a new ticket soon.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Marting,

I have downloaded the files with *.sal you have posted, but I do not know how to open the file.

BTW, as you know that the I3C requires ACK which is driven by receiver, so I suggest you test on the LPC5536-EVK board, do you test on the LPC5536-EVK board or your target board which has I3C master and slave?

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjun_rong,

To open the captures I shared, you must use the Saleae Logic Software. It is free and you can download it here: https://www.saleae.com/downloads/

Respect the hardware, I am using the LPCXpresso55S36 board acting the LPC5536 MCU as master and the ICM on-board sensor as a slave together with an external IMU (also as a slave). Do you need to know the serial number or revision number?

BR,

Martin